## ECLIPSE MV/10000<sup>™</sup> System Functional Characteristics

#### **Notice**

Data General Corporation (DGC) has prepared this document for use by DGC personnel, customers, and prospective customers. The information contained herein shall not be reproduced in whole or in part without DGC's prior written approval.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARD-WARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFORMATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

CEO, DASHER, DATAPREP, ECLIPSE, ENTERPRISE, INFOS, microNOVA, NOVA, PROXI, SUPERNOVA, ECLIPSE MV/4000, ECLIPSE MV/6000, ECLIPSE MV/8000, TRENDVIEW, MANAP, and PRESENT are U.S. registered trademarks of Data General Corporation, and AZ-TEXT, DG/L, ECLIPSE MV/10000, GW/4000, GDC/1000, REV-UP, SWAT, XODIAC, GENAP, DEFINE, SLATE, microECLIPSE, BusiPEN, BusiGEN, and BusiTEXT are U.S. trademarks of Data General Corporation.

Ordering No. 014-000724

© Data General Corporation, 1983

All Rights Reserved

Printed in the United States of America

Rev. 00, April 1983

#### **Preface**

This book describes the functional characterisitics of the ECLIPSE MV/10000<sup>TM</sup> computer system. It is aimed at assembly language programmers familiar with *Principles of Operation*, 32-bit ECLIPSE® Systems (DGC No. 014-000704) and ECLIPSE® C/350 Principles of Operation (DGC No. 014-000610). For ease of use, this manual maps by chapter to Principles of Operation, 32-bit ECLIPSE® Systems.

#### **Manual Organization**

This manual has nine chapters and seven appendices.

Chapter 1, "Technical Summary," explains the system components and functions available on the ECLIPSE  $MV/10000^{TM}$  computer.

Chapter 2, "Fixed-Point Instruction Summary," summarizes fixed-point formats and instructions.

Chapter 3, "Floating-Point Instruction Summary," summarizes floating-point formats and instructions.

Chapter 4, "Stack Management Instruction Summary," summarizes the wide stack instructions.

Chapter 5, "Program Flow Management," explains program flow, interrupt handling, and fault handling.

Chapter 6, "Queue Management Instruction Summary," summarizes the queue instructions.

Chapter 7, "Device Management," describes the ECLIPSE MV/10000 I/O devices and applicable instructions.

Chapter 8, "Memory and System Management," presents the ECLIPSE MV/10000 privileged instructions and related information for the operating system designer.

Chapter 9, "C/350 Programming," discusses ECLIPSE C/350 programming compatibility.

Appendix A lists the instructions unique to the ECLIPSE MV/10000 computer alphabetically.

Appendix B presents the typical execution time for each ECLIPSE MV/10000 instruction.

Appendix C presents tabular data for the various programmer-accessible registers.

Appendix D lists the reserved memory locations for page zero and shows the formats for the context block.

Appendix E lists standard Data General I/O device codes.

Appendix F is a tabulation of the contents of Accumulator 1 for protection and nonprotection faults.

Appendix G describes the operation of and format for the Load Control Store instruction.

#### **Related Manuals**

Other manuals useful in conjunction with the MV/10000 are as follows:

Principles of Operation, 32-Bit ECLIPSE® Systems, Programmer's Reference Series (DGC No. 014-000704)

ECLIPSE® C/350, Principles of Operation (DGC No. 014-000610)

ECLIPSE® MV/10000, Product Summary Series (DGC No. 014-000737)

ECLIPSE® MV/Family Instruction Reference Booklet (DGC No. 014-000702)

Intelligent Asynchronous Controller, Programmer's Reference Series (DGC No. 014-000703)

Data General Communications Subsystems, Product Summary Series (DGC No. 014-000635)

Programmer's Reference Manual -- Peripherals (DGC No. 015-000021)

Learning to Use AOS/VS (DGC No. 093-006931)

AOS/VS Macroassembler Reference Manual (DGC No. 093-000242)

AOS/VS Programmer's Manual (DGC No. 093-000241)

#### **Conventions and Abbreviations**

facd

This manual uses the following conventions and abbreviations:

| []                             | Square brackets indicate an optional argument. Omit the square brackets when you include an optional argument with an Assembler statement.                                                              |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARGUMENT                       | Uppercase characters indicate a literal argument in an Assembler statement. When you include a literal argument with an Assembler statement, use the exact form.                                        |

| argument<br>and/or<br>argument | Lowercase or italic characters indicate a variable argument in an Assembler statement. When you include the argument with an Assembler statement, substitute a literal value for the variable argument. |

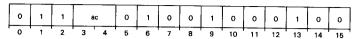

| ac                             | Indicates a fixed-point accumulator.                                                                                                                                                                    |

| acs                            | Indicates a source fixed-point accumulator.                                                                                                                                                             |

| acd                            | Indicates a destination fixed-point accumulator.                                                                                                                                                        |

| fac                            | Indicates a floating-point accumulator.                                                                                                                                                                 |

| facs                           | Indicates a source floating-point accumulator.                                                                                                                                                          |

Indicates a destination floating-point accumulator.

## Table of Contents

| 1 | Preface                                                           |            |

|---|-------------------------------------------------------------------|------------|

|   | Manual Organization Related Manuals Conventions and Abbreviations | i<br>ii    |

| 1 | Technical Summary                                                 |            |

|   | System Overview                                                   | 1-1        |

|   | Central Processing Unit                                           | 1-2        |

|   | Instruction Processor                                             | 1-2        |

|   | Arithmetic Processor                                              | 1-3        |

|   | Address Translator                                                | 1-3        |

|   | Memory System                                                     | 1-4        |

|   | System Cache                                                      | 1-4        |

|   | Memory Modules                                                    | 1-5        |

|   | I/O System                                                        | 1-6        |

|   | I/O Transfers                                                     | 1-6        |

|   | Communications Controllers                                        | 1-6        |

|   | Universal Power Supply Controller                                 | 1-7        |

|   | System Control Processor C/350 Compatibility                      | 1-7<br>1-8 |

|   | Registers                                                         | 1-6<br>1-8 |

|   | Initialization                                                    | 1-8        |

| 2 | Fixed-Point Instruction Summary                                   |            |

|   | Fixed-Point Data Formats                                          | 2-1        |

|   | Fixed-Point Instructions                                          | 2-2        |

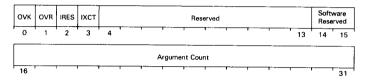

|   | Processor Status Register                                         | 2-8        |

|   | Decimal/Byte Operations                                           | 2-8        |

| 3 | Floating-Point Instruction Summary                                |            |

|   | Floating-Point Data Formats                                       | 3-1        |

|   | Floating-Point Instructions                                       | 3-2        |

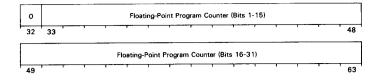

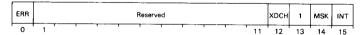

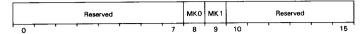

|   | Floating-Point Status Register                                    | 3-5        |

| 4 | Stack Management Instruction Summary                              | 4-1        |

| 5        | Program Flow Management                   |              |

|----------|-------------------------------------------|--------------|

|          | Program Flow Instructions                 | 5-1          |

|          | Instruction Addressing                    | 5-3          |

|          | Interrupt Handling                        | 5-4          |

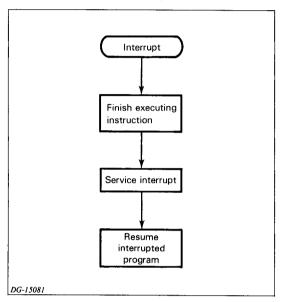

|          | Noninterruptible Instructions             | 5-5          |

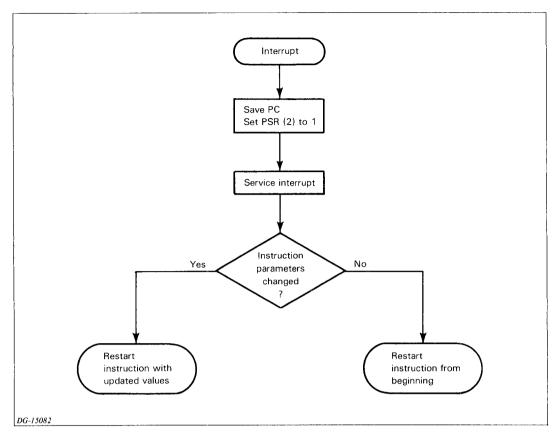

|          | Restartable Instructions                  | 5-5          |

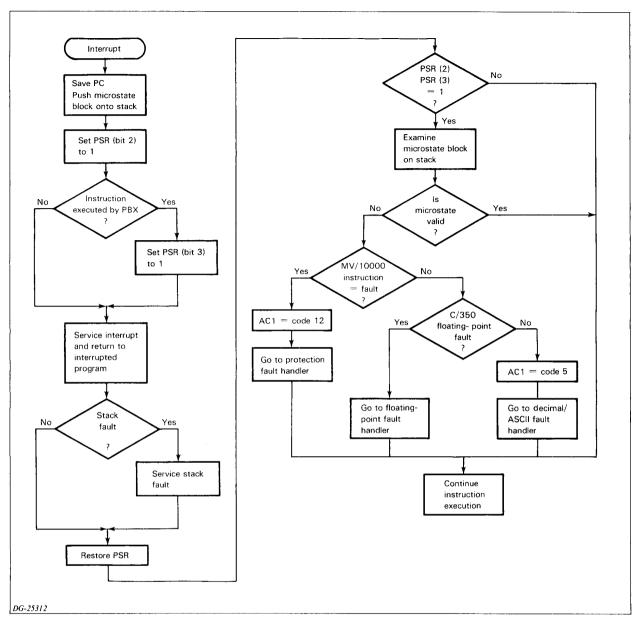

|          | Resumable Instructions                    | 5-6          |

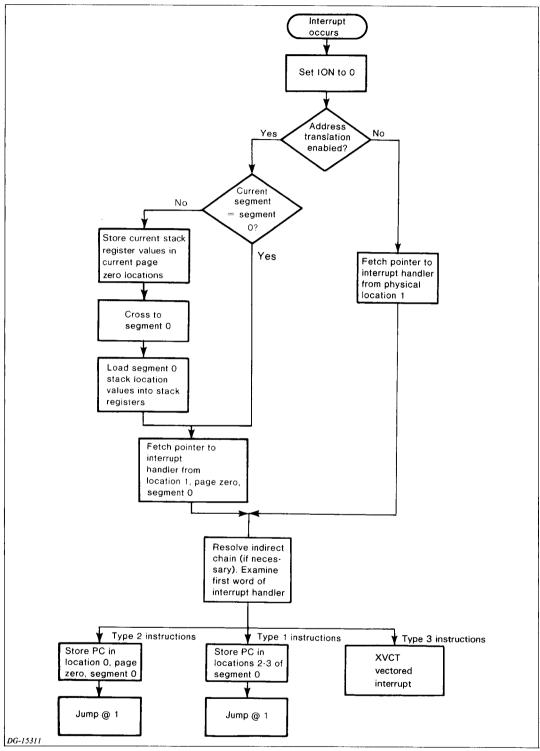

|          | Servicing an Interrupt                    | 5-7          |

|          | Fault Handling                            | 5-10         |

|          | Privileged Faults<br>Nonprivileged Faults | 5-10<br>5-10 |

| 6        | Queue Management Instruction Summary      | 3-10         |

|          | Device Management                         |              |

| <u>-</u> | General I/O Instructions                  | 7-1          |

|          | Central Processor                         | 7-1<br>7-2   |

|          | Device Flags                              | 7-2          |

|          | CPU Instructions                          | 7-2          |

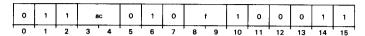

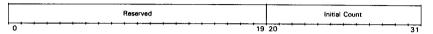

|          | Programmable Interval Timer               | 7-3<br>7-7   |

|          | Device Flags                              | 7-8          |

|          | PIT Instructions                          | 7-8          |

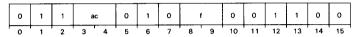

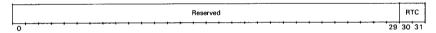

|          | Real-Time Clock                           | 7-9          |

|          | Device Flags                              | 7-9          |

|          | RTC Instructions                          | 7-10         |

|          | Primary Asynchronous Line Input/Output    | 7-10         |

|          | Device Flags TTI/TTO Instructions         | 7-11         |

|          | System Control Processor                  | 7-11         |

|          | Device Flags                              | 7-12<br>7-12 |

|          | SCP Instructions                          | 7-12         |

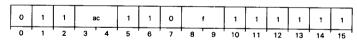

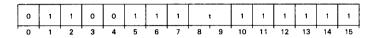

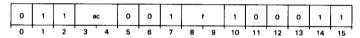

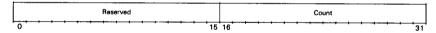

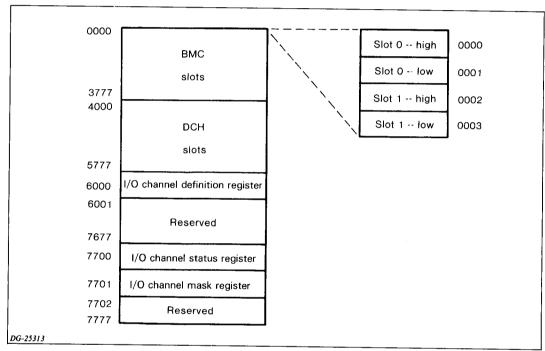

|          | Data Channel/Burst Multiplexor Channel    | 7-18         |

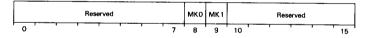

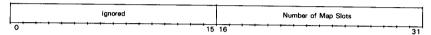

|          | DCH/BMC Maps                              | 7-18         |

|          | DCH/BMC Registers                         | 7-19         |

|          | DCH/BMC Map Instructions                  | 7-23         |

|          | Universal Power Supply Controller         | 7-25         |

|          | Device Flags                              | 7-25         |

|          | UPSC Instructions                         | 7-25         |

| 8        | Memory and System Management              |              |

|          | Address Translator                        | 8-1          |

|          | Referenced and Modified Bits              | 8-2          |

|          | Protection Validation                     | 8-2          |

|          | Memory/System Management Instructions     | 8-3          |

|          | Privileged Faults Page Faults             | 8-3          |

|          | Protection Faults                         | 8-3          |

|          | Reserved Memory                           | 8-5<br>8-5   |

| 9        | C/350 Programming                         |              |

|          | Registers                                 | 9-1          |

|          | Instruction Compatibility                 | 9-2          |

|          | Program Flow                              | 9-5          |

|          | Fault Handling                            | 9-5          |

|          | Reserved Memory                           | 9-6          |

|          | CPU Identification                        | 9-6          |

| A            | Instruction Summary                                 | A-1        |

|--------------|-----------------------------------------------------|------------|

| B            | Instruction Execution Times                         | B-1        |

| C            | Register Fields                                     |            |

|              | Program Counter                                     | C-1        |

|              | Processor Status Register                           | C-2        |

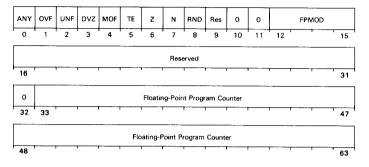

|              | Floating-Point Status Register                      | C-2        |

|              | Segment Base Registers                              | C-3        |

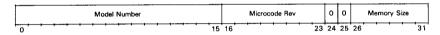

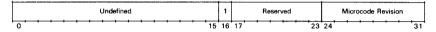

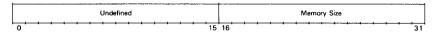

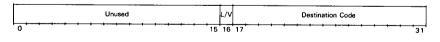

|              | DCH/BMC Status Registers CPU Identification         | C-4<br>C-5 |

|              | LCPID and ECLID Instructions                        | C-5<br>C-5 |

|              | NCLID Instruction                                   | C-6        |

|              |                                                     | C-0        |

| $\mathbf{D}$ | Reserved Memory Locations and Context Block Formats |            |

|              | Reserved Memory Locations                           | D-1        |

|              | Page Zero Locations for Segment 0                   | D-1        |

|              | Page Zero Locations for Segments 1 through 7        | D-3        |

|              | Context Block Formats                               | D-3        |

|              | CB State Format                                     | D-5        |

|              | IP State Format ATU State Format                    | D-5        |

|              | ALU State Format                                    | D-5        |

|              | MSEQ State Format                                   | D-5        |

|              | MDLQ State 1 offiliae                               | D-5        |

| E            | Standard I/O Device Codes                           | E-1        |

| F            | Fault Codes                                         |            |

| _            | Protection Faults                                   | F-1        |

|              | Page Faults                                         | F-2        |

|              | Stack Faults                                        | F-2        |

|              | Decimal/ASCII Faults UPSC Faults                    | F-3        |

|              | UPSC Faults                                         | F-4        |

| G            | Load Control Store Instruction                      |            |

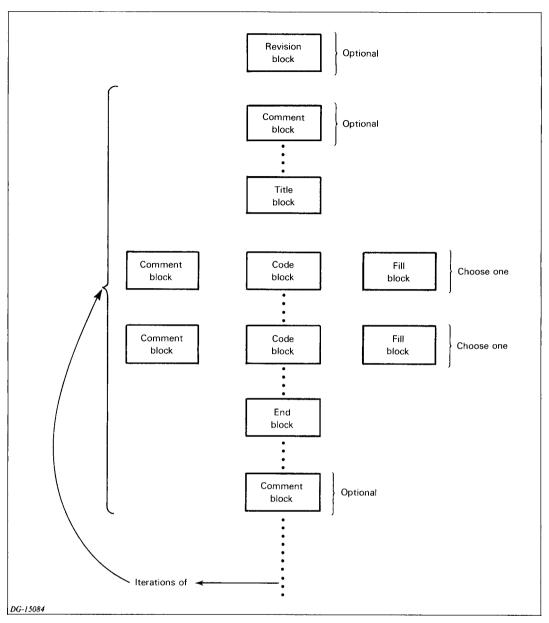

|              | Microcode File Format                               | G-2        |

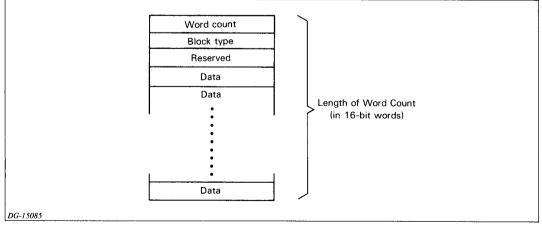

|              | Microcode Block Format                              | G-3        |

|              | LCS Implementation                                  | G-4        |

|              | Microcode Blocks<br>Error Return                    | G-4        |

|              | Kernel Functionality                                | G-7        |

|              | Reflict Lunctionality                               | G-9        |

## Illustrations

| 1.1         | The ECLIPSE MV/10000 system                         | 1-2  |

|-------------|-----------------------------------------------------|------|

| 1.2         | Memory, system cache, and instruction cache mapping | 1-4  |

| 1.3         | System cache during memory reference                | 1-5  |

| 5.1         | Noninterruptible instruction interrupt sequence     | 5-5  |

| 5.2         | Restartable instruction interrupt sequence          | 5-6  |

| 5.3         | Resumable instruction interrupt sequence            | 5-8  |

| 5.4         | Accessing the interrupt handler                     | 5-9  |

| 7.1         | DCH/BMC registers                                   | 7-20 |

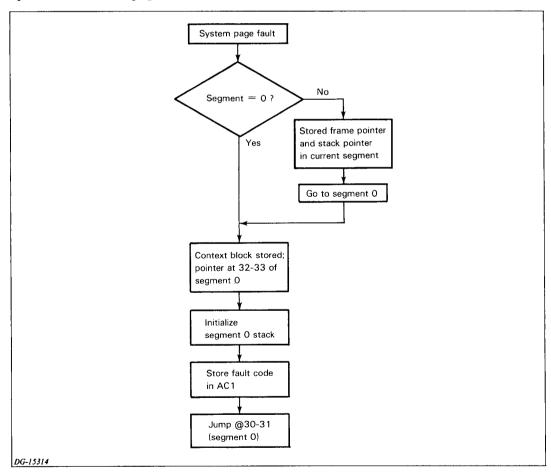

| 8.1         | Page fault sequence                                 | 8-4  |

| <b>G</b> .1 | Microcode file format                               | G-3  |

| G.2         | Microcode block form                                |      |

|             |                                                     | G-4  |

|  |  |  | . ) |

|--|--|--|-----|

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  | ì   |

|  |  |  |     |

|  |  |  | _   |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  | 1   |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

## **Tables**

| 2-1         | Fixed-point precision conversion                                | 2-2        |

|-------------|-----------------------------------------------------------------|------------|

| 2-2         | Fixed-point data movement instructions                          | 2-2        |

| 2-3         | Fixed-point addition instructions                               | 2-3        |

| 2-4         | Fixed-point subtraction instructions                            | 2-3        |

| 2-5         | Fixed-point multiplication instructions                         | 2-4        |

| 2-6         | Fixed-point division instructions                               | 2-4        |

| 2-7         | Initializing Carry instructions                                 | 2-4        |

| 2-8         | Fixed-point skip on condition instructions                      | 2-5        |

| 2-9         | Fixed-point increment or decrement word and skip instructions   | 2-6        |

| 2-10        | Logical instructions                                            | 2-6        |

| 2-11        | Logical shift instructions                                      | 2-7        |

| 2-12        | Fixed-point logical skip instructions                           | 2-7        |

| 2-13        | PSR manipulation instructions                                   | 2-8        |

| 2-14        | Fixed-point byte movement instructions                          | 2-8        |

| 2-15        | Fixed-point to floating-point conversion and store instructions | 2-9        |

| 2-16        | Load effective word and byte address instructions               | 2-9        |

| 2-17        | Edit subprogram instructions                                    | 2-9        |

| 2-18        | BCD arithmetic instructions                                     | 2-10       |

| 2-19        | Hex shift instructions                                          | 2-10       |

| 3-1         | Floating-point addition instructions                            | 3-2        |

| 3-2         | Floating-point subtraction instructions                         | 3-2        |

| 3-3         | Floating-point multiplication instructions                      | 3-2        |

| 3-4         | Floating-point division instructions                            | 3-3        |

| 3-5         | Floating-point skip on condition instructions                   | 3-3        |

| 3-6         | Floating-point binary conversion instructions                   | 3-3        |

| 3-7         | Floating-point decimal conversion instructions                  | 3-4        |

| 3-8         | Floating-point data movement instructions                       | 3-4        |

| 3-9         | FPSR instructions                                               | 3-5        |

| <b>4-</b> 1 | Wide stack register instructions                                | 4-1        |

| 4-2         | Wide stack double-word access instructions                      | 4-2        |

| 4-3         | Wide stack return block instructions                            | 4-2        |

| 4-4         | Multiword wide stack instructions                               | 4-3        |

| 5-1         | Execute accumulator instruction                                 | 5-1        |

| 5-2         | Jump instructions                                               | 5-1        |

| 5-3         | Skip instructions                                               | 5-2        |

| 5-4         | Subroutine instructions                                         | 5-2        |

| 5-5         | Segment transfer instructions                                   | 5-2        |

| 5-6         | Sequence of subroutine instructions                             | 5-3        |

| 5-7         | Restartable or resumable instructions                           | 5-4<br>5-7 |

| 5-8         | State of PSR bits 2 and 3                                       | 5-7<br>6-1 |

| 6-1         | Queue instructions                                              | 7-1        |

| 7-1         | General I/O instructions                                        | 7-1<br>7-2 |

| 7-2         | Device flags for general devices                                |            |

| 7-3         | Device flags for skip instruction                               | 7-2        |

| I/O instructions for CPU                                        | 7-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

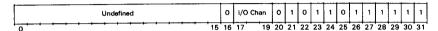

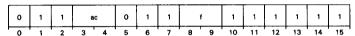

| CPU device instructions with I/O channels                       | 7-3<br>7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O instructions for PIT                                        | 7-4<br>7-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O instructions for RTC                                        | 7-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O instructions for TTI and TTO                                | 7-10<br>7-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

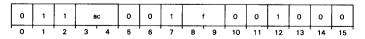

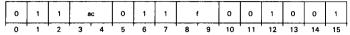

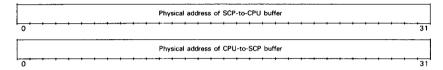

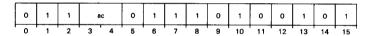

| SCP instructions                                                | 7-11<br>7-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                 | 7-13<br>7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

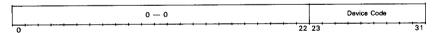

| DCH/BMC map instructions                                        | 7-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

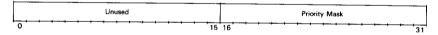

| I/O instructions for UPSC                                       | 7-25<br>7-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Memory and system management instructions                       | 8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C/350 fixed-point computing instructions                        | 9-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C/350 floating-point computing instructions                     | 9-3<br>9-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C/350 program flow management instructions                      | 9-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C/350 stack management instructions                             | · -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Page zero locations for segment 0                               | 9-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | D-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Context block format                                            | D-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Standard I/O device codes                                       | D-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | E-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | F-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | F-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | F-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | F-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table F 5 Universal power supply controller fault codes (octal) | F-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| continued                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| vontinuou                                                       | F-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                 | I/O instructions for CPU CPU device instructions with I/O channels I/O instructions for PIT I/O instructions for RTC I/O instructions for TTI and TTO SCP instructions Device map registers 0000-7777 DCH/BMC map instructions I/O instructions for UPSC Memory and system management instructions C/350 fixed-point computing instructions C/350 program flow management instructions C/350 program flow management instructions C/350 stack management instructions Page zero locations for segment 0 Page zero locations for segments 1 through 7 Context block format Standard I/O device codes Protection fault codes Page fault codes Decimal and ASCII fault codes Universal power supply controller fault codes (octal) Table F.5 Universal power supply controller fault codes (octal), continued |

# Chapter 1 Technical Summary

This chapter introduces the ECLIPSE  $MV/10000^{TM}$  computer system and describes initial processor conditions.

The ECLIPSE MV/10000<sup>TM</sup> computer system is a general-purpose 32-bit data processing system that supports the complete 32-bit instruction set described in *Principles of Operation, 32-Bit* ECLIPSE® *Systems* (DGC No. 014-000704). In addition, the ECLIPSE MV/10000 computer system retains substantial hardware and software compatibility with 16-bit ECLIPSE® systems. (Kernel 16-bit operating system instructions such as SYC, VCT, and LMP are not supported.)

The MV/10000 system operates in the manner described in *Principles of Operation*, 32-Bit ECLIPSE® Systems.

#### **System Overview**

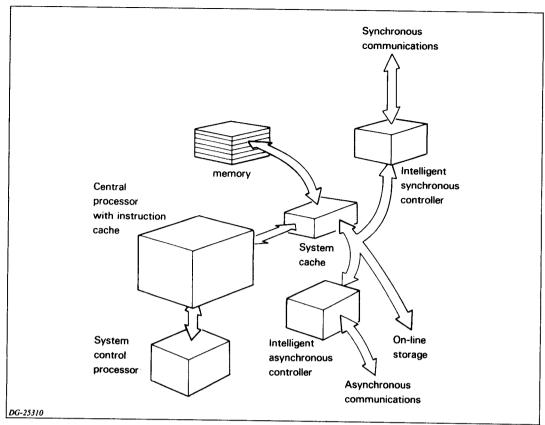

The physical MV/10000 system, shown in Figure 1.1, incorporates four main systems:

- The central processing unit (CPU), which consists of the instruction processor for decoding and executing instructions; the arithmetic processor for manipulation of data; and the address translator for logical to physical address translation.

- The *memory system*, which consists of a system cache that contains 1024 16-byte blocks and functions as a look-ahead/look-behind buffer; and up to eight memory modules of 2 Mbytes each.

- The *input/output system*, which consists of two I/O channels that support distributed processors for asynchronous and synchronous communications.

- The system control processor (SCP), a soft system console that performs diagnostic and operator-controlled functions.

Figure 1.1 The ECLIPSE MV/10000 system

#### **Central Processing Unit**

The CPU of the MV/10000 system executes all user programs and translates all virtual memory references into physical addresses. The CPU consists of a pipelined instruction processor, a high-speed arithmetic processor, a microsequencer, an address generator, and an address translator.

#### **Instruction Processor**

The instruction processor decodes instructions for execution. Its main component is the instruction cache, which provides input to the instruction decoder.

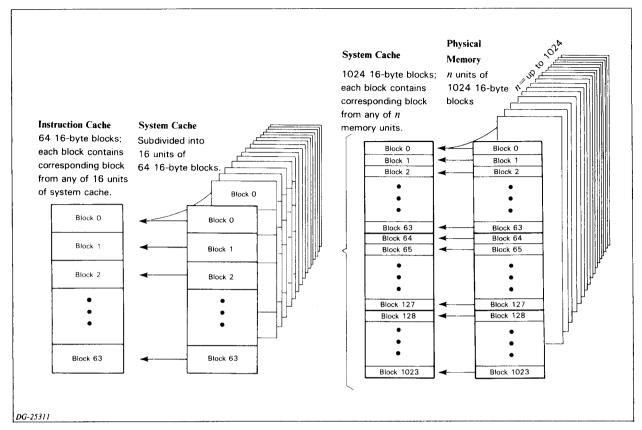

The 4-Kbyte instruction cache has 256 16-byte blocks and maps directly to the system cache. (See Figure 1.2 in the section entitled "Memory System.")

The 16 bytes of the instruction cache blocks correspond to the 16 bytes of the system cache blocks. The instruction cache block contains specific information: block 0 can contain any block 0 in the system cache, block 1 can contain any block 1 in the system cache, and so on.

Because of its look-ahead/look-behind capability, the instruction cache speeds program execution.

To execute an instruction, the instruction processor performs the following four steps:

- 1. Fetches an instruction from the instruction cache.

- 2. Parses the instruction opcode to obtain the starting address of the microcode routine and collects operand information.

- 3. Fetches the microinstruction and performs any effective addressing required.

- 4. Executes the microinstruction.

Four instructions — one instruction per step — can be in the pipeline at any one time.

#### **Arithmetic Processor**

The arithmetic processor manipulates floating-point numbers, fixed-point quantities, and addresses.

The MV/10000 system contains four 32-bit fixed-point accumulators. The ECLIPSE C/350 16-bit fixed-point accumulators correspond to bits 16 through 31 of the MV/10000 accumulators.

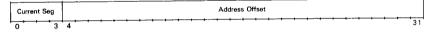

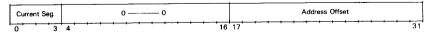

The program counter (PC) is 31 bits wide. Bits 1 through 3 specify the current segment of execution, and bits 4 through 31 specify an address in the segment.

Four floating-point accumulators, each 64 bits wide, contain the sign, the exponent, and the mantissa of a single- or double-precision floating-point operand. These four registers are identical to the C/350 floating-point registers. The MV/10000 floating-point status register (FPSR) is 64 bits wide.

Four 32-bit registers govern the MV/10000 wide stack: the wide stack pointer (WSP), the wide frame pointer (WFP), the wide stack limit (WSL), and the wide stack base (WSB). Maintaining the stack in hardware speeds up stack management operations.

#### Address Translator

The MV/10000 system has 4 Gbytes of logical memory and up to 16 Mbytes of physical memory. Because the logical address space is so much larger than the physical address space, the MV/10000 computer stores logical memory on disk in 2-Kbyte units called pages. When a process needs a page on disk, it moves the page to physical memory for manipulation. This page-swapping system is called a demand-page system. The MV/10000 system also contains an address translator that converts the logical address of a piece of data into a physical address in memory.

To avoid referring to a page table for every memory reference, the address translator maintains a table of address translations and access privileges for 1024 recently referenced pages — 128 per segment.

The address translator controls two memory management bits for each page: the *modified bit* and the *referenced bit*. The operating system uses these bits during *page faults*. (See Chapter 8 for a discussion of page faults.)

The address translator performs all the hardware checks required by the protection system. These checks include access validation, page validation, and ring crossing validation. If any of the checks fails, the address translator initiates a protection fault to the operating system. For more information on protection checks, refer to *Principles of Operation*, 32-bit ECLIPSE® Systems.

Figure 1.2 Memory, system cache, and instruction cache mapping

#### **Memory System**

The MV/10000 memory system is block-oriented. This means that the system elements expect and manipulate uniform data sizes and formats. These elements transfer data to one another in 16-byte blocks (four successive double words).

The major elements of the memory system are the system cache and the memory modules.

#### **System Cache**

The system cache functions as both a look-ahead and a look-behind buffer for the system, reducing the time that both the CPU and the input/output (I/O) system need to access main memory.

The system cache contains 1024 16-byte blocks, each directly mapped to main memory locations. This means that any block in the system cache can contain 16 contiguous bytes from main memory. Note that the system cache blocks cannot contain arbitrary locations from memory.

The memory consists of up to 1024 units, each unit containing 1024 16-byte blocks. Block 0 in the system cache can contain block 0 of any unit in main memory; block 1 in the system cache can contain block 1 of any unit in main memory; and so on. Figure 1.2 illustrates memory, system cache, and instruction cache mapping.

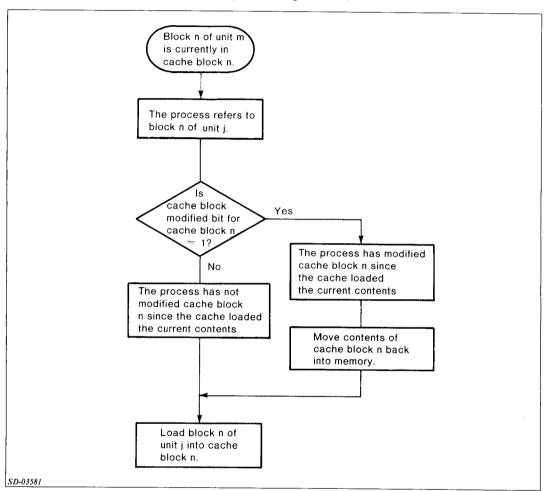

When a process makes a memory reference to block n of unit m in main memory, the system cache loads the 16-byte memory block containing the referenced data into system

cache block n. This memory block remains in the system cache until the process makes a new memory reference to block n of some other unit in main memory — for example, unit j.

When a process makes a reference to block n of unit j, the system cache examines the cache block modified bit of block n of unit m (the block currently in the cache). If the cache block modified bit is 1, the system cache writes block n of unit m back into main memory and then loads the new block n of unit j into system cache block n. If the cache block modified bit is 0, the system cache overwrites the current contents of system cache block n with those of block n of unit j. (See Figure 1.3.)

Figure 1.3 System cache during memory reference

The memory system contains two ports: one for the CPU and one for direct transfers between memory and the I/O system. The organization of the system cache is such that simultaneous data transfers can occur both between main memory and the CPU and between main memory and the I/O subsystem.

#### **Memory Modules**

The MV/10000 system supports up to eight dynamic random-access memory (RAM) modules of 2 Mbytes each. Each module contains 512K double words; each double word is 4 bytes long.

Every memory module consists of two independent planes, each containing 1 Mbyte. Each plane contains every other double word. With a 2-Mbyte memory module, for example, plane 0 contains the double words 0-1 and 4-5; plane 1 contains the double words 2-3 and 6-7; and so on. This arrangement allows memory operations on consecutive double words to overlap.

The MV/10000 computer transfers data at a rate of 57.1 Mbytes per second.

#### I/O System

The MV/10000 I/O system is electrically compatible and program compatible with the ECLIPSE C/350 and the MV/Family processors. This means that the MV/10000 computer supports the full family of standard Data General peripherals with high-speed burst multiplexor channel (BMC) I/O, data channel (DCH) I/O, and programmed I/O (PIO).

The MV/10000 I/O system supports two I/O channels and two I/O channel controllers. Each controller maintains one of the I/O channels, and each I/O channel contains its own BMC, DCH, and PIO I/O facilities. The MV/10000 I/O instructions allow you to communicate with peripherals on the I/O channels — either individually on one I/O channel or simultaneously on both I/O channels. For further information, refer to Chapter 7.

#### I/O Transfers

Both the BMC and the data channel transfer data to and from the system cache directly; data does not pass through the processor. The BMC transfers blocks of data to and from memory at a rate of up to 10.0 Mbytes per second on output and up to 14.2 Mbytes per second on input. The data channel operates at rates up to 1.4 Mbytes per second on output and 2.0 Mbytes per second on input.

Information can move between the system cache and the I/O channel board at a maximum rate of 28.6 Mbytes per second. Even at this rate, the CPU can continue unabated.

The programmed I/O system, working with a process, transfers words or parts of words between the processor accumulators and I/O devices. These transfers are instrumental in setting up the parameters for the higher speed channels. The MV/10000 computer executes all C/350 programmed I/O instructions exactly as the ECLIPSE C/350 does.

#### **Communications Controllers**

Two processors control the asynchronous and synchronous communications. The intelligent asynchronous controller (IAC) monitors asynchronous communications, and the intelligent synchronous controller (ISC) monitors synchronous communications.

#### **Intelligent Asynchronous Controller**

The IAC is a 16-bit processor connected to the MV/10000 computer. It features standard facilities such as accumulators, stacks, an I/O bus, an ECLIPSE C/350 instruction subset, and a priority interrupt system. Each IAC supports either 8 (IAC/8) or 16 (IAC/16) asynchronous communications lines. The MV/10000 computer can support a total of 192 asynchronous lines.

The MV/10000 central processor and the IAC must communicate to coordinate their operation. For example, the IAC must signal the host when it has completed a task or needs more information. The IAC memory allocation and protection unit and two groups of special instructions provide the MV/10000 computer and the IAC with the necessary ability to communicate.

For further information, refer to Intelligent Asynchronous Controller, Programmer's Reference Series.

#### **Intelligent Synchronous Controller**

The intelligent synchronous controller (ISC) — a 16-bit processor connected to the MV/10000 computer — features standard facilities such as accumulators, stacks, an I/O bus, an ECLIPSE instruction subset, and a priority interrupt system. The ISC handles two asynchronous or synchronous communications lines.

The ISC memory allocation and protection unit and two groups of special instructions provide the MV/10000 computer and the ISC with the ability to communicate.

#### **Universal Power Supply Controller**

The universal power supply controller (UPSC) is a microprocessor-controlled power system that performs diagnostic functions. The UPSC performs a power-up diagnostic self test; monitors the system power; and reports failures, problems, and status information to the MV/10000 computer. The UPSC is programmable and responds to a request for status information. If programmed to do so, it can also generate an interrupt request.

For more information on the UPSC, see Chapter 7.

#### **System Control Processor**

The system control processor (SCP) is a system within the MV/10000 computer and has its own microcomputer. That is, the SCP has its own CPU and its own operating system. The SCP is a soft system console. It performs diagnostic functions and loads microcode into the microsequencer.

As a soft console, the SCP performs system control functions under operator control. It permits the operator to load or examine and modify main memory and to single-step through a program, instruction by instruction.

As a diagnostic tool, the SCP runs programs designed to help isolate hardware problems. It also maintains an error log. When an error occurs, the SCP records the type of error, its location, and the time it occurred.

The SCP provides all the system timing for the MV/10000 system. It also connects to other components via several buses to allow examination and modification of internal registers.

The operator terminal of the SCP gives the operator control over the MV/10000 system by transmitting commands to the system and providing direct responses and reports.

The SCP also contains the real-time clock, the programmable interval timer, and the primary asynchronous line, all of which appear to the main processor to be I/O devices.

For further information on the SCP, see Chapter 7.

#### C/350 Compatibility

The MV/10000 computer supports the instruction mnemonics and binary opcodes of most instructions implemented on the ECLIPSE C/350. This means that most programs that execute on the C/350 computer will also execute on the MV/10000 computer without recompiling or reassembling.

Several C/350 instructions manipulate data between accumulators without referring to memory. You do not have to modify these instructions to use them in MV/10000-system-specific programs.

Principles of Operation, 32-Bit ECLIPSE® Systems describes the compatibility of C/350 and 32-bit instructions, data types, and formats.

Appendix A lists MV/10000-specific instructions.

#### **Registers**

The MV/10000 system implements the following registers.

- four 64-bit floating-point accumulators

- four 32-bit fixed-point accumulators

- one 32-bit processor status register

- one 64-bit floating-point status register

- four 32-bit stack management registers

- one 31-bit program counter

- eight 32-bit segment base registers

For more information on these registers, see *Principles of Operation, 32-Bit* ECLIPSE® *Systems*.

#### **Initialization**

The processor assumes the physical mode upon power-up, a system reset, or the execution of the *Reset* instruction (IORST).

The processor performs the following functions when it first powers up (and the system microcode loads) or after a system reset:

- Disables logical address translation, which means that logical and physical addresses are equal.

- Keeps the logical address translation protection system in force. That is, the protection system functions as if ring 0 were the current ring of execution.

- Does not initialize the values of the referenced and modified bits. (The values are indeterminate.)

- Sets the processor status register (PSR) and bits 0 through 9 of the floating-point status register (FPSR) to 0.

- Disables error reporting.

- Does not initialize data channel maps. (Data channel maps are undefined.)

- Sets the I/O channel mask bit for channel 1 to a 1.

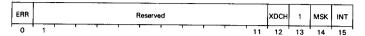

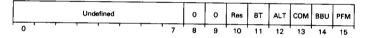

- Sets bits 3, 4, 7, 8, 9, and 14 of the I/O channel definition register.

- Halts

After the execution of the *Reset* instruction, the processor performs the following actions:

- Disables logical address translation.

- Keeps the logical address translation protection system in force.

- Sets the PSR and bits 0 through 9 of the FPSR to 0.

- Disables error reporting.

- Disables data channel maps and places itself in physical mode.

When in physical mode, effective address translation works the same way it does when logical address translation is enabled. However, because the logical address space exceeds the physical address space in size, the processor truncates a number of the 31 most significant bits of the logical address before referring to memory. The number of bits truncated depends on the amount of physical memory available. The maximum length of the word address formed from this procedure will be 25 bits for 16 Mbytes of physical memory.

|  |  | i |

|--|--|---|

|  |  |   |

## Chapter 2

### Fixed-Point Instruction Summary

This chapter summarizes the data formats and instructions for fixed-point and decimal/byte operations and lists the instructions used to manipulate the processor status register (PSR). For further information, refer to *Principles of Operation*, 32-Bit ECLIPSE® Systems.

#### **Fixed-Point Data Formats**

This section presents the fixed-point accumulator formats for the 16- and 32-bit two's complement numbers and the 16- and 32-bit logical numbers.

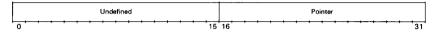

# Zero or Sign Extend S Two's Complement Number 31 32-Bit Fixed-Point Two's Complement Format Two's Complement Number 15 16-Bit Fixed-Point Logical Format Undefined Undefined Logical Data 15 16 31 32-Bit Fixed-Point Logical Format

16-Bit Fixed-Point Two's Complement Format

#### **Fixed-Point Instructions**

Tables 2.1 through 2.12 list the fixed-point instructions.

| Instruction | Function                       |

|-------------|--------------------------------|

| CVWN        | Convert from 32-bit to 16-bit  |

| SEX         | Sign extend 16 bits to 32 bits |

| ZEX         | Zero extend 16 bits to 32 bits |

Table 2.1 Fixed-point precision conversion

| Instruction | Function                                            |

|-------------|-----------------------------------------------------|

| LDATS       | Load accumulator with double word addressed by WSP  |

| LNLDA       | Narrow load accumulator                             |

| LNSTA       | Narrow store accumulator                            |

| LWLDA       | Wide load accumulator                               |

| LWSTA       | Wide store accumulator                              |

| MOV *       | Move and skip                                       |

| NLDAI       | Narrow load immediate                               |

| STATS       | Store accumulator into double word addressed by WSP |

| WBLM        | Wide block move                                     |

| WLDAI       | Wide load with wide immediate                       |

| WMOV        | Wide move                                           |

| WPOP        | Wide pop accumulators                               |

| WPSH        | Wide push accumulators                              |

| WXCH        | Wide exchange accumulators                          |

| XCH *       | Exchange accumulators                               |

| XNLDA       | Narrow load accumulator                             |

| XNSTA       | Narrow store accumulator                            |

| XWLDA       | Wide load accumulator                               |

| XWSTA       | Wide store accumulator                              |

Table 2.2 Fixed-point data movement instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                              |

|-------------|---------------------------------------|

| ADC *       | Add complement and skip               |

| ADD *       | Add and skip                          |

| ADDI *      | Extended add immediate                |

| ADI *       | Add immediate                         |

| INC *       | Increment and skip                    |

| LNADD       | Narrow add memory word to accumulator |

| LNADI       | Narrow add immediate                  |

| LWADD       | Wide add memory word to accumulator   |

| LWADI       | Wide add immediate ·                  |

| NADD        | Narrow add                            |

| NADDI       | Narrow extended add immediate         |

| NADI        | Narrow add immediate                  |

| WADC        | Wide add complement                   |

| WADD        | Wide add                              |

| WADDI       | Wide add with wide immediate          |

| WADI        | Wide add immediate                    |

| WINC        | Wide increment (no skip)              |

| WNADI       | Wide add with narrow immediate        |

| XNADD       | Narrow add accumulator to memory word |

| XNADI       | Narrow add immediate                  |

| XWADD       | Wide add memory word to accumulator   |

| XWADI       | Wide add immediate                    |

Table 2.3 Fixed-point addition instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                    |

|-------------|-----------------------------|

| LNSBI       | Narrow subtract immediate   |

| LNSUB       | Narrow subtract memory word |

| LWSBI       | Wide subtract immediate     |

| LWSUB       | Wide subtract memory word   |

| NSBI        | Narrow subtract immediate   |

| NSUB        | Narrow subtract             |

| SBI *       | Subtract immediate          |

| SUB *       | Subtract and skip           |

| WSBI        | Wide subtract immediate     |

| WSUB        | Wide subtract               |

| XNSBI       | Narrow subtract immediate   |

| XNSUB       | Narrow subtract memory word |

| XWSBI       | Wide subtract immediate     |

| XWSUB       | Wide subtract memory word   |

Table 2.4 Fixed-point subtraction instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                    |  |

|-------------|-----------------------------|--|

| LNMUL       | Wide multiply memory word   |  |

| LWMUL       | Wide multiply memory word   |  |

| MUL *       | Unsigned multiply           |  |

| MULS *      | Signed multiply             |  |

| NMUL        | Narrow sign extend multiply |  |

| WMUL        | Wide multiply               |  |

| WMULS       | Wide signed multiply        |  |

| XNMUL       | Narrow multiply memory word |  |

| XWMUL       | Wide multiply memory word   |  |

Table 2.5 Fixed-point multiplication instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                  |

|-------------|---------------------------|

| DIV *       | Unsigned divide           |

| DIVS *      | Signed divide             |

| DIVX *      | Sign extend and divide    |

| HLV *       | Halve (AC/2)              |

| LNDIV       | Narrow divide memory word |

| LWDIV       | Wide divide memory word   |

| NDIV        | Narrow sign extend divide |

| WDIV        | Wide divide               |

| WDIVS       | Wide signed divide        |

| WHLV        | Wide halve                |

| XNDIV       | Narrow divide memory word |

| XWDIV       | Wide divide memory word   |

Table 2.6 Fixed-point division instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                                            |

|-------------|-----------------------------------------------------|

| ADC*        | Add complement with optional Carry initialization   |

| ADD*        | Add with optional Carry initialization              |

| AND*        | AND with optional Carry initialization              |

| COM*        | One's complement with optional Carry initialization |

| CRYTC       | Complement Carry                                    |

| CRYTO       | Set Carry bit to 1                                  |

| CRYTZ       | Set Carry bit to 0                                  |

| INC*        | Increment with optional Carry initialization        |

| MOV*        | Move with optional Carry initialization             |

| NEG*        | Negate with optional Carry initialization           |

| SUB*        | Subtract with optional Carry initialization         |

Table 2.7 Initializing Carry instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                                                 |

|-------------|----------------------------------------------------------|

| ADC*        | Add complement with optional skip                        |

| ADD*        | Add with optional skip                                   |

| INC *       | Increment with optional skip                             |

| MOV *       | Move with optional skip                                  |

| NSALA       | Narrow skip on all bits set in accumulator               |

| NSALM       | Narrow skip on all bits set in memory location           |

| NSANA       | Narrow skip on any bit set in accumulator                |

| NSANM       | Narrow skip on any bit set in memory location            |

| SGE *       | Skip if ACS greater than or equal to ACD                 |

| SGT *       | Skip if ACS greater than ACD                             |

| SNOVR       | Skip on OVR reset                                        |

| SUB *       | Subtract with optional skip                              |

| WCLM        | Wide compare to limits and skip                          |

| WSALA       | Wide skip on all bits set in accumulator                 |

| WSALM       | Wide skip on all bits set in double word memory location |

| WSANA       | Wide skip on any bit set in accumulator                  |

| WSANM       | Wide skip on any bit set in double word memory location  |

| WSEQ        | Wide skip if ACS equal to ACD                            |

| WSEQI       | Wide skip if equal to immediate                          |

| WSGE        | Wide signed skip if ACS greater than or equal to ACD     |

| WSGT        | Wide signed skip if ACS greater than ACD                 |

| WSGTI       | Wide skip if AC greater than immediate                   |

| WSKBO       | Wide skip on AC bit set to 1                             |

| WSKBZ       | Wide skip on AC bit set to 0                             |

| WSLE        | Wide signed skip if ACS less than or equal to ACD        |

| WSLEI       | Wide skip if AC less than or equal to immediate          |

| WSLT        | Wide signed skip if ACS less than ACD                    |

| WSNB        | Wide skip on addressed bit set to 1                      |

| WSNE        | Wide skip if ACS not equal to ACD                        |

| WSNEI       | Wide skip if AC not equal to immediate                   |

| WSZB        | Wide skip on addressed bit set to 0                      |

| WSZBO       | Wide skip on addressed bit set to 0 and set bit to 1     |

| WUGTI       | Wide unsigned skip if AC greater than immediate          |

| WULEI       | Wide unsigned skip if AC less than or equal to immediate |

| WUSGE       | Wide unsigned skip if ACS greater than or equal to ACD   |

| WUSGT       | Wide unsigned skip if ACS greater than ACD               |

Table 2.8 Fixed-point skip on condition instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                                               |  |

|-------------|--------------------------------------------------------|--|

| DSZTS       | Decrement the double word addressed by WSP (skip if 0) |  |

| INC *       | Increment and skip                                     |  |

| ISZTS       | Increment the double word addressed by WSP (skip if 0) |  |

| LNDSZ       | Narrow decrement and skip if 0                         |  |

| LNISZ       | Narrow increment and skip if 0                         |  |

| LWDSZ       | Wide decrement and skip if 0                           |  |

| LWISZ       | Wide increment and skip if 0                           |  |

| XNDSZ       | Narrow decrement and skip if 0                         |  |

| XNISZ       | Narrow increment and skip if 0                         |  |

| XWDSZ       | Wide decrement and skip if 0                           |  |

| XWISZ       | Wide increment and skip if 0                           |  |

Table 2.9 Fixed-point increment or decrement word and skip instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Function                           |

|-------------|------------------------------------|

| ANC *       | AND with complemented source       |

| AND *       | AND                                |

| ANDI *      | AND immediate                      |

| COM *       | Complement                         |

| IOR *       | Inclusive OR                       |

| IORI *      | Inclusive OR immediate             |

| LOB *       | Locate lead bit                    |

| LRB *       | Locate and reset lead bit          |

| NEG *       | Negate                             |

| NNEG        | Narrow negate                      |

| WANC        | Wide AND with complemented source  |

| WAND        | Wide AND                           |

| WANDI       | Wide AND immediate                 |

| WBTO        | Wide set bit to 1                  |

| WBTZ        | Wide set bit to 0                  |

| WCOB        | Wide count bits                    |

| WCOM        | Wide complement (one's complement) |

| WIOR        | Wide inclusive OR                  |

| WIORI       | Wide inclusive OR immediate        |

| WLOB        | Wide locate lead bit               |

| WLRB        | Wide locate and reset lead bit     |

| WLSN        | Wide load sign                     |

| WNEG        | Wide negate                        |

| WXOR        | Wide exclusive OR                  |

| WXORI       | Wide exclusive OR immediate        |

| XOR *       | Exclusive OR                       |

| XORI *      | Exclusive OR immediate             |

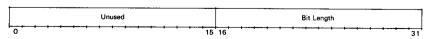

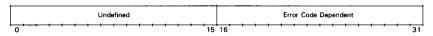

Table 2.10 Logical instructions