**Customer Documentation**

# **ECLIPSE MV/9500™ System** Principles of Operation

**Customer Documentation**

# ECLIPSE MV/9500<sup>™</sup> System Principles of Operation Supplement

|  |  | - |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

# ECLIPSE MV/9500<sup>™</sup> System Principles of Operation Supplement

014-001855-00

Ordering No. 014-001855 Copyright © Data General Corporation, 1990 All Rights Reserved Printed in the United States of America Rev. 00, March, 1990

#### **Notice**

DATA GENERAL CORPORATION (DGC) HAS PREPARED THIS DOCUMENT FOR USE BY DGC PERSONNEL, CUSTOMERS, AND PROSPECTIVE CUSTOMERS. THE INFORMATION CONTAINED HEREIN SHALL NOT BE REPRODUCED IN WHOLE OR IN PART WITHOUT DGC'S PRIOR WRITTEN APPROVAL.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARDWARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFORMATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

CEO, DASHER, DATAPREP, DESKTOP GENERATION, ECLIPSE, ECLIPSE MV/4000, ECLIPSE MV/6000, ECLIPSE MV/8000, GENAP, INFOS, microNOVA, NOVA, PRESENT, PROXI, SWAT, and TRENDVIEW are U.S. registered trademarks of Data General Corporation; and AOSMAGIC, AOS/VSMAGIC, AROSE/PC, ArrayPlus, AViiON, BaseLink, BusiGEN, BusiPEN, BusiTEXT, CEO Connection, CEO Connection/LAN, CEO Drawing Board, CEO DXA, CEO Light, CEO MAILI, CEO Object Office, CEO PXA, CEO Wordview, CEOwrite, COBOL/SMART, COMPUCALC, CSMAGIC, DASHER/One, DASHER/286, DASHER/386, DASHER/LN, DATA GENERAL/One, DESKTOP/UX, DG/500, DG/AROSE, DGConnect, DG/DBUS, DG/Fontstyles, DG/GATE, DG/GEO, DG/HEO, DG/L, DG/LIBRARY, DG/UX, DG/XAP, ECLIPSE MV/1000, ECLIPSE MV/1400, ECLIPSE MV/2000, ECLIPSE MV/2500, ECLIPSE MV/7800, ECLIPSE MV/9500, ECLIPSE MV/10000, ECLIPSE MV/15000, ECLIPSE MV/18000, ECLIPSE MV/20000, ECLIPSE MV/40000, FORMA-TEXT, GATEKEEPER, GDC/1000, GDC/2400, microECLIPSE, microMV, MV/UX, PC Liaison, RASS, REV-UP, SLATE, SPARE MAIL, SUPPORT MANAGER, TEO, TEO/3D, TEO/Electronics, TURBO/4, UNITE, WALKABOUT, WALKABOUT/SX, and XODIAC are trademarks of Data General Corporation.

ECLIPSE MV/9500<sup>™</sup> System Principles of Operation Supplement 014-001855-00

Revision History:

Original Release - March 1990

## **Updating Instructions**

The complete documentation for ECLIPSE MV/9500<sup>TM</sup> Systems Principles of Operation consists of the two-volume set, ECLIPSE<sup>®</sup> MV/Family (32-Bit) Systems Principles of Operation (014-001371) and ECLIPSE<sup>®</sup> MV/Family (32-Bit) Systems Instruction Dictionary (014-001372), and this supplement (014-001855).

To create your copy of the ECLIPSE MV/9500 specific manual, please remove the following pages from the ECLIPSE® MV/Family (32-Bit) Systems Principles of Operation and ECLIPSE® MV/Family (32-Bit) Systems Instruction Dictionary and insert the supplement pages as follows:

| Remove (from 014-001371) | Insert (from 014-001855)             |

|--------------------------|--------------------------------------|

| _                        | Title/Notice (before Title/Notice of |

|                          | 014-001371)                          |

| Contents                 | Contents                             |

| Figures                  | Figures                              |

| Tables                   | Tables                               |

| 1-17/1-18                | 1–17 through 1–30                    |

| 8-1/8-2                  | 8-1/8-2                              |

| 8-9/8-10                 | 8-9/8-10                             |

| 8-21/8-22                | 8-21/8-22                            |

| 8-25 through 8-28        | 8-25 through 8-28                    |

| 8-35/8-36                | 8-35/8-36                            |

| 8-59/8-60                | 8-59/8-60                            |

| 8-71 through 8-80        | 8-71 through 8-80                    |

| 8-93                     | 8-93                                 |

| A-7/A-8                  | A-7 through A-9                      |

| _                        | Appendix E                           |

| _                        | Appendix F                           |

| _                        | Appendix G                           |

| Index                    | Index                                |

| Front Cover              | New Front Cover for 014-001371       |

|                          | (at end of supplement)               |

| Back Cover               | New Back Cover for 014-001371        |

|                          | (at end of supplement)               |

| Remove (from 014-001372) | Insert (from 014-001855)             |

| None                     | None                                 |

|  |  | - |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

# **Contents**

| System Overview                        |

|----------------------------------------|

| Functional Capabilities                |

| Registers                              |

| Fixed-Point Computation                |

| Floating-Point Computation             |

| Stack Management                       |

| Program Flow Management                |

| Queue Management                       |

| Graphics Management                    |

| Device Management                      |

| System Management                      |

| Memory Management                      |

| ECLIPSE 16-Bit Compatible Instructions |

|                                        |

| Accessing Memory                       |

| Current Segment                        |

| Other Segments                         |

| Memory Reference Instructions          |

| Address Modes                          |

| Operand Access                         |

| Protection Capabilities                |

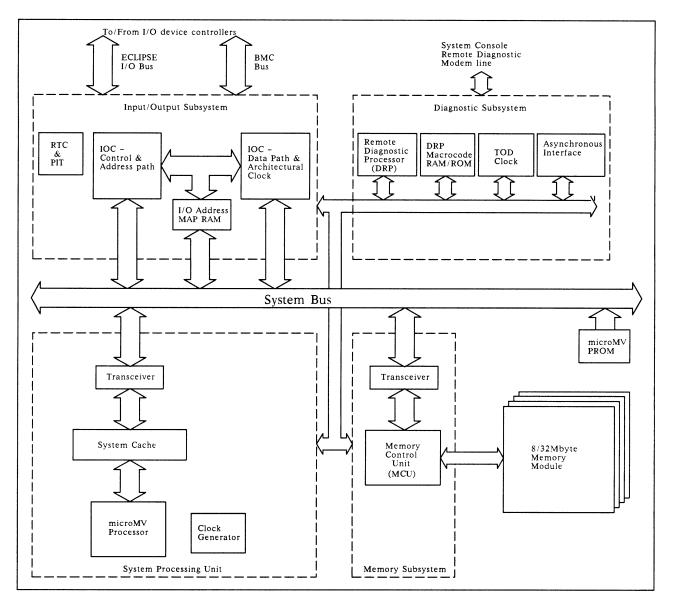

| ECLIPSE MV/9500™ Hardware Summary      |

| Main Systems                           |

| Central Processing Unit                |

| Memory System                          |

| Input/Output System                    |

| Power System                           |

| Diagnostic Remote Processor            |

| Initialization                         |

| Fixed-Point Computing                  |

| Binary Operations                      |

| Data Formats                           |

| Move Instructions                      |

| Arithmetic Instructions                |

| Carry Operations                       |

| Shift Instructions                     |

| Skip Instructions                      |

| •                                      |

| Overflow Fault                         |

| Processor Status Register              |

| Logical Operations                     |

| Data Formats                           |

| Logical Instructions                   |

| Bit Manipulation                       |

| Shift Instructions                     |

| Skip Instructions                      |

|   | Decimal and Byte Operations Data Formats Move Instructions Arithmetic Instructions Shift Instructions Effective Address Instructions Skip Instructions Data Type Faults Decimal Arithmetic Example                                                                                                                                                                       | 2-15<br>2-15<br>2-19<br>2-20<br>2-21<br>2-21<br>2-22<br>2-23                                     |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 3 | Floating-Point Computing                                                                                                                                                                                                                                                                                                                                                 |                                                                                                  |

|   | Data Formats Conversion Instructions Move Instructions Floating-Point Arithmetic Operations Appending Guard Digits Aligning the Mantissas Calculating and Normalizing the Result Truncating or Rounding the Result Storing the Result Arithmetic Instructions Addition Subtraction Multiplication Division Skip Instructions Intrinsic Instruction Set Faults and Status | 3-2<br>3-3<br>3-4<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-8<br>3-9<br>3-10<br>3-12 |

| 4 | Stack Management                                                                                                                                                                                                                                                                                                                                                         |                                                                                                  |

|   | Wide Stack Operations Wide Stack Registers Wide Stack Base Wide Stack Limit Wide Stack Pointer Wide Frame Pointer Wide Stack Register Instructions Wide Stack Data Instructions Initializing a Wide Stack Wide Stack Faults                                                                                                                                              | 4-2<br>4-3<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-7<br>4-8                                      |

| 5 | Program Flow Management                                                                                                                                                                                                                                                                                                                                                  |                                                                                                  |

|   | Related Instruction Groups  Execute Accumulator  Jump  Skip  Subroutine  Transferring Program Control to Another Segment  Subroutine Call  Subroutine Return  Fault Handling  Fixed-Point Overflow Fault  Floating-Point Faults  Decimal and ASCII Data Faults  Stack Faults                                                                                             | 5-2<br>5-2<br>5-2<br>5-2<br>5-4<br>5-9<br>5-14<br>5-16<br>5-17<br>5-18<br>5-19                   |

| 6 | Queue Management                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                              |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|   | Building a Queue Queue Descriptor Setting Up and Modifying a Queue Queue Examples Queue Descriptor of an Empty Queue Adding a Data Element into an Empty Queue Adding a Data Element at the Head of a Queue Adding a Data Element at the Tail of a Queue Removing a Data Element Queue Instructions                                                                | 6-2<br>6-3<br>6-3<br>6-3<br>6-4<br>6-4<br>6-4<br>6-6                                                                         |

| 7 | Graphics Management                                                                                                                                                                                                                                                                                                                                                |                                                                                                                              |

|   | Graphics Instruction Set  Forms Forms and Bitmaps Local Origin Bounding Rectangle Coordinate System  GIS Data Structures Form Descriptor  Form Attributes Operation Mask and Combination Rule Line Drawing Attributes Character Drawing Attributes Character Fonts Cursor Descriptor Color Descriptors  Form Cache Interrupts  Fault Handling Fixed-Point Overflow | 7-2 7-4 7-5 7-6 7-6 7-7 7-9 7-9 7-13 7-13 7-16 7-17 7-17 7-20 7-21 7-21 7-22 7-25                                            |

| 8 | Device Management  I/O Communication                                                                                                                                                                                                                                                                                                                               | 8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-8<br>8-8<br>8-9<br>8-10<br>8-12<br>8-17<br>8-22<br>8-25<br>8-29<br>8-29<br>8-32<br>8-33 |

| Integral Devices Central Processor Timing Mechanisms Architectural Clocks Programmable Interval Timer Real-Time Clock Primary Asynchronous Line Input/Output System Control Processor/Program Power Supply Controllers Multiple Central Processing Units Initialization                                                                                       | 8-36<br>8-49<br>8-49<br>8-60<br>8-63             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Timing Mechanisms  Architectural Clocks  Programmable Interval Timer  Real-Time Clock  Primary Asynchronous Line Input/Output  System Control Processor/Program  Power Supply Controllers  Multiple Central Processing Units                                                                                                                                  | 8-49<br>8-49<br>8-60<br>8-63                     |

| Architectural Clocks                                                                                                                                                                                                                                                                                                                                          | 8-49<br>8-60<br>8-63                             |

| Programmable Interval Timer Real-Time Clock Primary Asynchronous Line Input/Output System Control Processor/Program Power Supply Controllers Multiple Central Processing Units                                                                                                                                                                                | 8-60<br>8-63                                     |

| Real-Time Clock                                                                                                                                                                                                                                                                                                                                               | 8-63                                             |

| Primary Asynchronous Line Input/Output  System Control Processor/Program  Power Supply Controllers  Multiple Central Processing Units                                                                                                                                                                                                                         |                                                  |

| System Control Processor/Program  Power Supply Controllers  Multiple Central Processing Units                                                                                                                                                                                                                                                                 |                                                  |

| Power Supply Controllers                                                                                                                                                                                                                                                                                                                                      |                                                  |

| Multiple Central Processing Units                                                                                                                                                                                                                                                                                                                             |                                                  |

|                                                                                                                                                                                                                                                                                                                                                               |                                                  |

| Initialization                                                                                                                                                                                                                                                                                                                                                |                                                  |

|                                                                                                                                                                                                                                                                                                                                                               |                                                  |

| Processor State Block                                                                                                                                                                                                                                                                                                                                         |                                                  |

| Memory Views                                                                                                                                                                                                                                                                                                                                                  |                                                  |

| I/O Communication                                                                                                                                                                                                                                                                                                                                             |                                                  |

| Multiple I/O Channels                                                                                                                                                                                                                                                                                                                                         |                                                  |

| I/O Interrupt Handling                                                                                                                                                                                                                                                                                                                                        |                                                  |

| Intra-Processor Communication                                                                                                                                                                                                                                                                                                                                 |                                                  |

| Error Codes                                                                                                                                                                                                                                                                                                                                                   | 8–93                                             |

|                                                                                                                                                                                                                                                                                                                                                               |                                                  |

| 9 Memory and System Management                                                                                                                                                                                                                                                                                                                                |                                                  |

| D A                                                                                                                                                                                                                                                                                                                                                           | 9–2                                              |

| Page Access                                                                                                                                                                                                                                                                                                                                                   |                                                  |

| Segment Access and Address Translation                                                                                                                                                                                                                                                                                                                        | 9-2                                              |

| Segment Base Registers                                                                                                                                                                                                                                                                                                                                        |                                                  |

| Page Frames                                                                                                                                                                                                                                                                                                                                                   |                                                  |

| Pagetables                                                                                                                                                                                                                                                                                                                                                    |                                                  |

| Address Translation                                                                                                                                                                                                                                                                                                                                           |                                                  |

| Page Access                                                                                                                                                                                                                                                                                                                                                   |                                                  |

| Central Processor Identification                                                                                                                                                                                                                                                                                                                              |                                                  |

| Privileged Faults                                                                                                                                                                                                                                                                                                                                             | 9–11                                             |

| Page Faults                                                                                                                                                                                                                                                                                                                                                   | 9–11                                             |

| Protection Violations                                                                                                                                                                                                                                                                                                                                         |                                                  |

| Reserved Memory                                                                                                                                                                                                                                                                                                                                               | 9-18                                             |

| Page Zero                                                                                                                                                                                                                                                                                                                                                     |                                                  |

| State Area                                                                                                                                                                                                                                                                                                                                                    | 9–21                                             |

|                                                                                                                                                                                                                                                                                                                                                               |                                                  |

|                                                                                                                                                                                                                                                                                                                                                               |                                                  |

| 10 ECLIPSE 16-Bit Programming                                                                                                                                                                                                                                                                                                                                 |                                                  |

| •                                                                                                                                                                                                                                                                                                                                                             | 10-2                                             |

| ECLIPSE Registers                                                                                                                                                                                                                                                                                                                                             |                                                  |

| ECLIPSE Registers                                                                                                                                                                                                                                                                                                                                             | 10-5                                             |

| ECLIPSE Registers                                                                                                                                                                                                                                                                                                                                             | 10-5<br>10-6                                     |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program                                                                                                                                                                                                                                                                 | 10-5<br>10-6<br>10-6                             |

| ECLIPSE Registers                                                                                                                                                                                                                                                                                                                                             | 10-5<br>10-6<br>10-6<br>10-7                     |

| ECLIPSE Registers                                                                                                                                                                                                                                                                                                                                             | 10-5<br>10-6<br>10-6<br>10-7<br>10-7             |

| ECLIPSE Registers                                                                                                                                                                                                                                                                                                                                             | 10-5<br>10-6<br>10-6<br>10-7<br>10-7             |

| ECLIPSE Registers                                                                                                                                                                                                                                                                                                                                             | 10-5<br>10-6<br>10-7<br>10-7<br>10-8<br>10-8     |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program  Expanding an ECLIPSE Subroutine  ECLIPSE Instructions  ECLIPSE Memory Reference Instructions  ECLIPSE Fixed-Point Instructions                                                                                                                                 | 10-5<br>10-6<br>10-7<br>10-7<br>10-8<br>10-12    |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program  Expanding an ECLIPSE Subroutine  ECLIPSE Instructions  ECLIPSE MV/Family Instruction Compatibility  ECLIPSE Memory Reference Instructions  ECLIPSE Fixed-Point Instructions  ECLIPSE Floating-Point Instructions                                               | 10-5 10-6 10-7 10-7 10-8 10-12 10-13             |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program  Expanding an ECLIPSE Subroutine  ECLIPSE Instructions  ECLIPSE MV/Family Instruction Compatibility  ECLIPSE Memory Reference Instructions  ECLIPSE Fixed-Point Instructions  ECLIPSE Floating-Point Instructions  ECLIPSE Program Flow Instructions            | 10-5 10-6 10-7 10-7 10-8 10-12 10-13 10-15       |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program  Expanding an ECLIPSE Subroutine  ECLIPSE Instructions  ECLIPSE Memory Reference Instructions  ECLIPSE Fixed-Point Instructions  ECLIPSE Floating-Point Instructions  ECLIPSE Program Flow Instructions  ECLIPSE Stack Instructions                             | 10-5 10-6 10-7 10-7 10-8 10-12 10-13 10-15       |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program  Expanding an ECLIPSE Subroutine  ECLIPSE Instructions  ECLIPSE Memory Reference Instructions  ECLIPSE Fixed-Point Instructions  ECLIPSE Floating-Point Instructions  ECLIPSE Program Flow Instructions  ECLIPSE Stack Instructions  ECLIPSE Stack Instructions | 10-5 10-6 10-7 10-7 10-8 10-12 10-13 10-15 10-16 |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program  Expanding an ECLIPSE Subroutine  ECLIPSE Instructions  ECLIPSE Memory Reference Instructions  ECLIPSE Fixed-Point Instructions  ECLIPSE Floating-Point Instructions  ECLIPSE Program Flow Instructions  ECLIPSE Stack Instructions                             | 10-5 10-6 10-7 10-7 10-8 10-12 10-13 10-15 10-16 |

| ECLIPSE Registers  ECLIPSE Stack  ECLIPSE Faults and Interrupts  Expanding an ECLIPSE Program  Expanding an ECLIPSE Subroutine  ECLIPSE Instructions  ECLIPSE Memory Reference Instructions  ECLIPSE Fixed-Point Instructions  ECLIPSE Floating-Point Instructions  ECLIPSE Program Flow Instructions  ECLIPSE Stack Instructions  ECLIPSE Stack Instructions | 10-5 10-6 10-7 10-7 10-8 10-12 10-15 10-17 10-17 |

| Α    | Register Fields                                                                                                                                                              |                                               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|      | Segment Base Registers  Program Counter  Processor Status Register  Floating-Point Status Register  DCH/BMC Status Registers  CPU Identification  ECLIPSE MV/9500 Supplement | A-2<br>A-3<br>A-4<br>A-5<br>A-6<br>A-7<br>A-9 |

| В    | Fault and Status Codes                                                                                                                                                       |                                               |

|      | Protection Faults Page Faults Stack Faults UPSC Faults PSC Status and Faults Decimal/ASCII Faults                                                                            | B-1<br>B-2<br>B-2<br>B-2<br>B-4<br>B-6        |

| С    | Reserved Memory Locations                                                                                                                                                    |                                               |

| D    | Load Control Store Instruction                                                                                                                                               |                                               |

|      | Microcode File and Block Format  LCS Implementation  Microcode Blocks  Error Return  Kernel Functions                                                                        | D-3<br>D-4<br>D-5<br>D-7<br>D-8               |

| E    | Standard I/O Device Codes                                                                                                                                                    |                                               |

| F    | Context Block Formats                                                                                                                                                        |                                               |

| G    | Instruction Execution Times                                                                                                                                                  |                                               |

| Glos | ssary                                                                                                                                                                        |                                               |

# **Figures**

| _ |    |   |   |   |

|---|----|---|---|---|

|   | i. | ^ |   | _ |

|   | 8  | ч | ч | c |

| 1-1  | ECLIPSE MV/Family functional components                       | 1-1  |

|------|---------------------------------------------------------------|------|

| 1-2  | Fixed-point accumulator                                       | 1-3  |

| 1-3  | Floating-point accumulator                                    | 1-4  |

| 1-4  | Program counter format                                        | 1-5  |

| 1-5  | Logical address space                                         | 1-7  |

| 1-6  | Memory reference instruction word addressing formats          | 1-10 |

| 1-7  | Memory reference instruction byte addressing formats          | 1-11 |

| 1-8  | Byte pointer format                                           | 1-15 |

| 1-9  | Byte addressing                                               | 1-16 |

| 1-10 | Bit pointer format                                            | 1-17 |

| 1-11 | Bit addressing                                                | 1-17 |

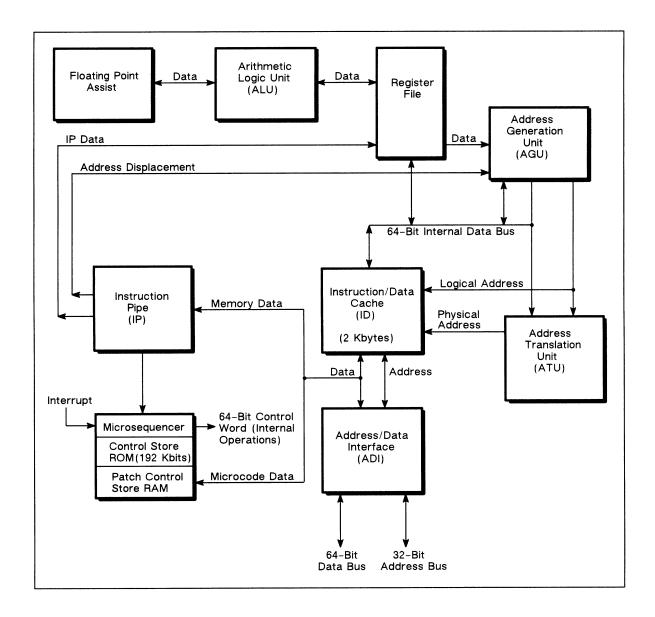

| 1-12 | Major elements of the ECLIPSE MV/9500 system                  | 1-20 |

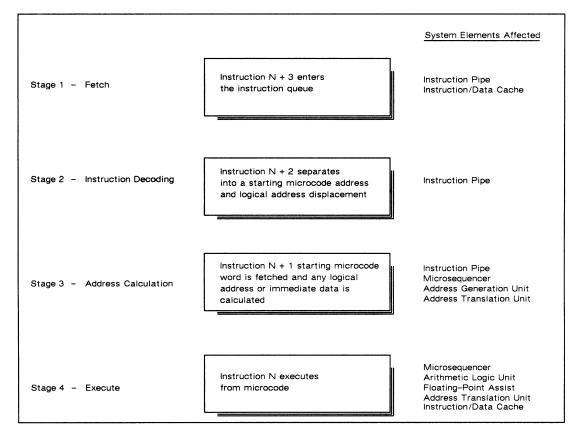

| 1-13 | Four-stage instruction pipeline                               | 1-21 |

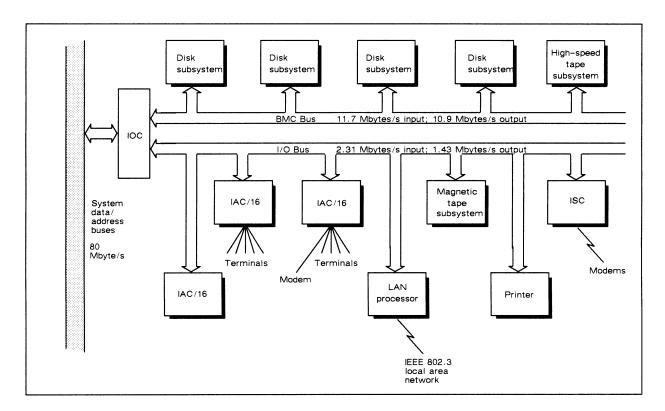

| 1-14 | I/O system                                                    | 1-26 |

| 1-15 | Diagnostic remote processor                                   | 1-29 |

| 2-1  | Fixed-point two's-complement data formats                     | 2-2  |

| 2-2  | ECLIPSE compatible shift operations                           | 2-8  |

| 2-3  | Processor status register format                              | 2-10 |

| 2-4  | Fixed-point logical data formats                              | 2-12 |

| 2-5  | Explicit data type indicator                                  | 2-15 |

| 2-6  | Packed and unpacked decimal data                              | 2-18 |

| 2-7  | Decimal arithmetic example                                    | 2-23 |

| 3-1  | Floating-point data formats                                   | 3-2  |

| 3-2  | Intrinsic instruction set format                              | 3-10 |

| 3-3  | Floating-point status register format                         | 3-13 |

| 4-1  | Typical wide stack                                            | 4-2  |

| 4-2  | Wide stack management register format                         | 4-3  |

| 4-3  | Sample code for initializing a wide stack                     | 4-7  |

| 4-4  | Example of wide stack operations                              | 4-7  |

| 5-1  | Illegal and legal skip instruction sequences                  | 5-3  |

| 5-2  | DO-loop instruction sequence                                  | 5-3  |

| 5-3  | Example of subroutine code for XJSR                           | 5-7  |

| 5-4  | Wide stack operations from XJSR, WSSVS, and XPEF instructions | 5-8  |

| 5-5  | Wide stack operations from WRTN instruction                   | 5-8  |

| 5-6  | Gate array format                                             | 5-10 |

| 5-7  | XCALL or LCALL effective address                              | 5-11 |

| 5-8  | Validating inward segment crossing sequence                   | 5-13 |

| 5_9  | Wide Return instruction sequence                              | 5-15 |

#### Figure

| 6-1  | Data elements with user data                             | 6-2   |

|------|----------------------------------------------------------|-------|

| 6-2  | Format of queue descriptor                               | 6-3   |

| 6-3  | Queue descriptor for an empty queue                      | 6-3   |

| 6-4  | Data element added to an empty queue                     | 6-4   |

| 6-5  | Data element added at head of queue                      | 6-4   |

| 6-6  | Data element added at tail of queue                      | 6-5   |

| 6-7  | Data element removed                                     | 6-6   |

| 7-1  | Form data structures                                     | 7-4   |

| 7-2  | Windowing with virtual bitmaps                           | 7-5   |

| 7-3  | Use of rectangle list                                    | 7-6   |

| 7-4  | Coordinate conversions                                   | 7-8   |

| 7-5  | Vertex of contiguous line segments                       | 7-16  |

| 7-6  | Effect of line style                                     | 7-17  |

| 7-7  | Types of cursors                                         | 7-18  |

| 7-8  | GIS fault sequence                                       | 7-23  |

| 7-9  | Overdraw condition parameters                            | 7-26  |

| 7-10 | Overdraw condition parameters for endpoints              | 7-27  |

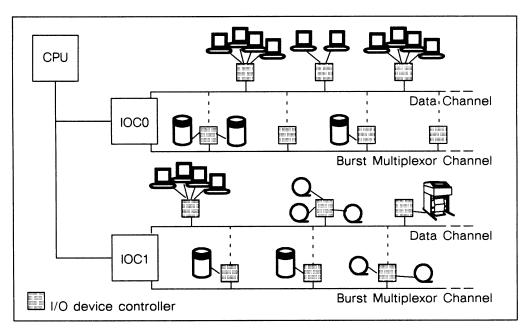

| 8-1  | An ECLIPSE MV/Family system with dual IOCs               | 8-2   |

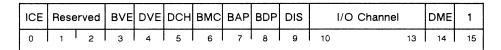

| 8-2  | General I/O instruction format                           | 8-6   |

| 8-3  | Interrupt sequence                                       | 8-11  |

| 8-4  | Vectored interrupt processing sequence                   | 8-13  |

| 8-5  | Sequence of actions to conclude interrupt service        | 8-14  |

| 8-6  | Vector table                                             | 8-14  |

| 8-7  | Device control table (DCT)                               | 8-16  |

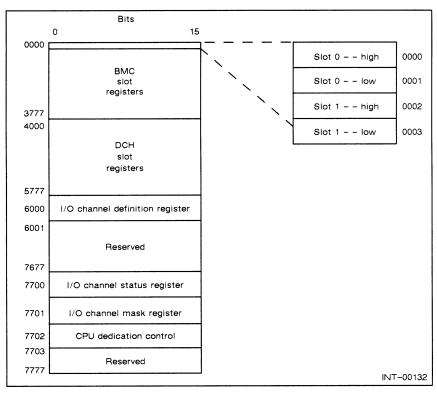

| 8-8  | DCH/BMC registers                                        | 8-25  |

| 8-9  | CPU/SCP communications sequence                          | 8-69  |

| 9-1  | Segment base register format                             | 9-3   |

| 9-2  | Pagetable entry format                                   | 9-4   |

| 9-3  | Indirect and effective logical address formats           | 9-6   |

| 9-4  | One-level pagetable translation                          | 9-7   |

| 9-5  | Two-level pagetable translation                          | 9-8   |

| 9-6  | Page fault sequence                                      | 9-12  |

| 9-7  | Protection violation sequence                            | 9-16  |

| 10-1 | ECLIPSE MV/Family registers with applicable ECLIPSE bits | 10-4  |

| 10-2 | ECLIPSE word addressing format                           | 10-8  |

| 10-3 | ECLIPSE effective addressing                             | 10-9  |

| 10-4 | ECLIPSE byte addressing format                           | 10-9  |

| 10-5 | ECLIPSE byte addressing                                  | 10-10 |

| 10-6 | ECLIPSE bit addressing format                            | 10-10 |

| 10-7 | BTO, BTZ, SNB, SZB, and SZBO bit addressing              | 10-11 |

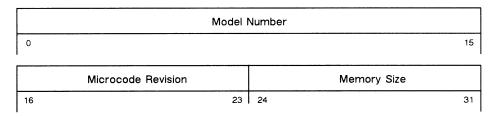

| D-1  | Microcode file format                                    | D-4   |

| D-2  | Microcode block format                                   | D-5   |

# **Tables**

| Table                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7                                                                                      | Program counter format  Effective addressing  Word-oriented data  Byte data  Byte pointer contents  Bit pointer contents  Faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13 2-14 2-15 2-16 2-17 2-18 2-19 2-20 2-21 2-22 2-23 2-24 2-25 2-26 2-27 2-28 | Fixed-point two's-complement formats Range of 16- and 32-bit fixed-point numbers (in octal) Fixed-point precision conversion Fixed-point data movement instructions Fixed-point addition instructions Fixed-point subtraction instructions Fixed-point multiplication instructions Fixed-point division instructions Fixed-point division instructions Fixed-point increment or decrement value and skip instructions Carry initializing instructions Fixed-point skip on condition instructions PSR manipulation instructions Processor status register contents Logical Instructions Bit Instructions Bit Instructions Logical shift instructions Fixed-point logical skip instructions Data type indicator description Explicit data types Sign and number combination for unpacked decimal Nonsign-positioned numbers for unpacked decimal Fixed-point byte movement instructions Fixed-point to floating-point conversion and store instructions Edit subprogram instructions Arithmetic instructions Hex shift instructions Load effective address instructions Decimal and ASCII fault codes |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8                                                                               | Floating-point data formats description  Floating-point binary conversion instructions  Floating-point decimal conversion instructions  Floating-point data movement instructions  Floating-point addition instructions  Floating-point subtraction instructions  Floating-point multiplication instructions  Floating-point division instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-9<br>3-10<br>3-11<br>3-12<br>3-13                                                                                                                                 | Floating-point skip on condition instructions Intrinsic instruction set format description 3. Floating-point intrinsic instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6                                                                                                                              | Wide stack management register format description Wide stack register instructions Wide stack doubleword access instructions Wide stack return block instructions Standard wide return block Instructions affecting the wide stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9<br>5-10<br>5-11<br>5-12<br>5-13<br>5-14<br>5-15<br>5-16<br>5-17<br>5-18<br>5-19<br>5-20<br>5-21<br>5-22 | Jump instructions Skip instructions Standard wide return block Subroutine instructions Sequence of subroutine instructions Segment program control transfer instructions Gate array format description  XCALL or LCALL effective address format description  Faults  Fixed-point fault return block  Wide floating-point fault return block  Narrow floating-point fault return block  Decimal and ASCII fault codes  Wide return block for decimal data fault (type 1)  Wide return block for ASCII data fault (type 2)  Wide return block for ASCII data fault (type 3)  Narrow return block for ASCII data fault (type 2)  Narrow return block for ASCII data fault (type 2)  Narrow return block for ASCII data fault (type 3)  Narrow return block for ASCII data fault (type 2)  Sample |

| 6-1                                                                                                                                                                 | Queue instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6<br>7-7                                                                                                                       | GIS instructions  Form descriptor contents  Rectangle descriptor contents  Form attributes  Combination rules  Cross-hair cursor descriptor  Image cursor descriptor  7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8                                                                                                                | General I/O instructions General I/O instruction format description Device flag controls for general devices Device flag tests for skip instruction Vector table contents Device control table contents  I/O instructions for DCH/BMC maps  8 I/O registers  8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

8-25

#### Table

| 8-9        | Word/block counter values                                        | 8-31       |

|------------|------------------------------------------------------------------|------------|

| 8-10       | I/O instructions for the CPU                                     | 8-37       |

| 8-11       | CPU device instructions with I/O channels                        | 8-40       |

| 8-12       | Instructions affecting the alarm clock                           | 8-50       |

| 8-13       | Instructions affecting the time-slice timer                      | 8-54       |

| 8-14       | Instructions affecting the PIT                                   | 8-60       |

| 8-15       | Instructions affecting the RTC                                   | 8-63       |

| 8-16       | I/O instructions for TTI and TTO                                 | 8-66       |

| 8-17       | SCP instructions                                                 | 8-68       |

| 8-18       | I/O instructions for the power supply controllers                | 8-81       |

| 8-19       | Multiple-processor instructions                                  | 8-92       |

| 8-20       | ECLIPSE MV/Family instructions with multiple-processor functions | 8-93       |

| 8-21       | Error values returned to AC1                                     | 8-93       |

| 0-21       |                                                                  | 0 73       |

| 9-1        | Segment base register format description                         | 9-3        |

| 9-2        | Pagetable entry format description                               | 9-5        |

| 9-3        | Logical address format description                               | 9-6        |

| 9-4        | Instructions that manipulate referenced and modified bits        | 9-10       |

| 9-5        | System identification instructions                               | 9-10       |

| 9-6        | Priority of protection violation faults                          | 9-13       |

| 9-7        | Protection fault return block                                    | 9-15       |

| 9-8        | Protection fault codes                                           | 9-15       |

| 9-9        | Page zero locations for segment 0                                | 9-19       |

| 9-10       | Page zero locations for segments 1 through 7                     | 9-20       |

|            |                                                                  |            |

| 10-1       | Comparison of ECLIPSE 16-bit and ECLIPSE MV/Family registers     | 10-3       |

| 10-2       | Standard ECLIPSE (narrow) return block                           | 10-5       |

| 10-3       | Alterations to ECLIPSE subroutines                               | 10-7       |

| 10-4       | ECLIPSE word addressing format description                       | 10-9       |

| 10-5       | ECLIPSE byte addressing format description                       | 10-9       |

| 10-6       | ECLIPSE bit addressing format description                        | 10-11      |

| 10-7       | ECLIPSE fixed-point computing instructions                       | 10-12      |

| 10-8       | ECLIPSE floating-point computing instructions                    | 10-13      |

| 10-9       | ECLIPSE program flow management instructions                     | 10-15      |

| 10-10      | ECLIPSE stack management instructions                            | 10-16      |

|            |                                                                  |            |

| A-1        | Registers and contents                                           | A-1        |

| A-2        | Segment base register contents                                   | A-2        |

| A-3        | Program counter format for ECLIPSE MV/Family programs            | A-3        |

| A-4        | Program counter modified by ECLIPSE 16-bit instructions          | A-3        |

| A-5        | Processor status register contents                               | A-4        |

| A-6        | Floating-point status register contents                          | A-5        |

| A-7        | I/O channel status register contents                             | A-6        |

| A-8        | I/O channel mask register contents                               | A-6        |

| A-9        | I/O channel definition register contents                         | A-7        |

| B-1        | Protection fault codes                                           | B-1        |

| B-2        | Page fault codes                                                 | B-1<br>B-2 |

| B-3        | Stack fault codes                                                | B-2<br>B-2 |

| в-3<br>В-4 | UPSC fault codes                                                 | B-2<br>B-2 |

| B-5        | PSC status and fault codes                                       | B-2<br>B-4 |

| в-3<br>В-6 | Decimal/ASCII fault codes                                        | B-4<br>B-6 |

| D_0        | Decimal/Asch laun cours                                          | D-0        |

#### Table

| C-1<br>C-2        | Page zero location for segment 0                       | C-2<br>C-3        |

|-------------------|--------------------------------------------------------|-------------------|

| D-1               | Microcode file format blocks                           | D-3               |

| D-2               | Words used in the microcode block format               | D-5               |

| D-3               | Title block format                                     | D-5               |

| D-4               | End block format                                       | D-6               |

| D-5               | Combined action of End block data words 1 and 2        | D-6               |

| D-6               | Code block format                                      | D-6               |

| D-7               | Fill block format                                      | D-7               |

| D-8               | Comment block format                                   | D-7               |

| D-9               | Revision block format                                  | D-7               |

| D-10              | Error codes returned to AC0                            | D-8               |

| E-1               | Standard I/O device codes                              | E-1               |

| F-1               | Context block format                                   | F-2               |

| G-1<br>G-2<br>G-3 | Adjusting memory references  Adjusting any instruction | G-1<br>G-1<br>G-4 |

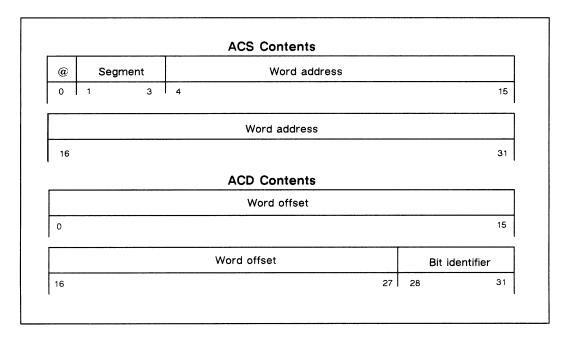

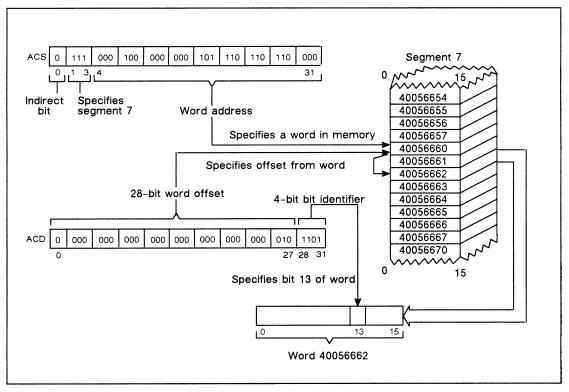

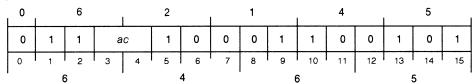

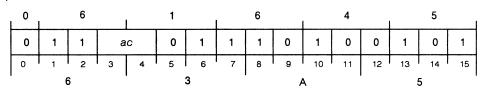

Figure 1-10 Bit pointer format

The processor uses the *acs* accumulator contents to calculate an effective address. If a bit instruction specifies the two accumulators as the same accumulator, then the base word address is zero in the current segment.

Figure 1-11 Bit addressing

### **Protection Capabilities**

While executing an instruction, the processor checks the validity of a memory reference or an I/O operation (protection violation), a page reference (nonresident page), a stack operation, a computation, and a data format. Table 1–7 lists the validity checks (or faults).

Table 1-7 Faults

| Fault                                | Туре          |  |

|--------------------------------------|---------------|--|

| Nonresident page                     | Privileged    |  |

| Protection violation                 | Privileged    |  |

| Stack operation                      | Nonprivileged |  |

| Fixed-point computation              | Nonprivileged |  |

| Floating-point computation           | Nonprivileged |  |

| Invalid decimal or ASCII data format | Nonprivileged |  |

If the processor detects an error, a nonprivileged or privileged fault occurs before the next instruction is executed. A nonprivileged fault occurs when the processor detects a computation error. The processor limits I/O access on a per ring basis, and limits memory access using a hierarchical protection mechanism. For instance,

- Before executing an I/O instruction, the processor checks the I/O validity flag in the current segment.

- Before executing a memory reference instruction, the processor checks the validity of the reference.

The processor executes an I/O or memory reference instruction when validity checks permit the access. Otherwise, the processor initiates a protection violation. Thus, an operating system can restrict access to the devices to specific segment(s).

Accessing and changing a protection mechanism requires a privileged instruction (executable only in segment 0) or data access, typically controlled by the operating system. Refer to the chapter, "Program Flow Management," for further details on servicing a nonprivileged fault.