**Customer Documentation**

# **Designing Interfaces for** the ECLIPSE® I/O Bus

# Designing Interfaces for the ECLIPSE® I/O Bus

014-001856-00

Ordering No. 014-001856 Copyright © Data General Corporation, 1990 All Rights Reserved Printed in the United States of America Rev. 00, January 1990

#### **Notice**

DATA GENERAL CORPORATION (DGC) HAS PREPARED THIS DOCUMENT FOR USE BY DGC PERSONNEL, CUSTOMERS, AND PROSPECTIVE CUSTOMERS. THE INFORMATION CONTAINED HEREIN SHALL NOT BE REPRODUCED IN WHOLE OR IN PART WITHOUT DGC'S PRIOR WRITTEN APPROVAL.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARDWARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFORMATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

CEO, DASHER, DATAPREP, DESKTOP GENERATION, ECLIPSE, ECLIPSE MV/4000, ECLIPSE MV/6000, ECLIPSE MV/8000, GENAP, INFOS, microNOVA, NOVA, PRESENT, PROXI, SWAT, and TRENDVIEW are U.S. registered trademarks of Data General Corporation; and AOSMAGIC, AOS/VSMAGIC, AROSE/PC, ArrayPlus, AVIION, BusiGEN, BusiPEN, BusiTEXT, CEO Connection, CEO Connection/LAN, CEO Drawing Board, CEO DXA, CEO Light, CEO MAILI, CEO Object Office, CEO PXA, CEO Wordview, CEOwrite, COBOL/SMART, COMPUCALC, CSMAGIC, DASHER/One, DASHER/286, DASHER/386, DASHER/LN, DATA GENERAL/One, DESKTOP/UX, DG/500, DG/AROSE, DGConnect, DG/DBUS, DG/Fontstyles, DG/GATE, DG/GEO, DG/HEO, DG/L, DG/LIBRARY, DG/UX, DG/XAP, ECLIPSE MV/1000, ECLIPSE MV/1400, ECLIPSE MV/2000, ECLIPSE MV/2500, ECLIPSE MV/7800, ECLIPSE MV/9500, ECLIPSE MV/10000, ECLIPSE MV/15000, ECLIPSE MV/18000, ECLIPSE MV/20000, ECLIPSE MV/40000, FORMA-TEXT, GATEKEEPER, GDC/1000, GDC/2400, microECLIPSE, microMV, MV/UX, PC Liaison, RASS, REV-UP, SLATE, SPARE MAIL, SUPPORT MANAGER, TEO, TEO/3D, TEO/Electronics, TURBO/4, UNITE, and XODIAC are trademarks of Data General Corporation.

Teflon is a U.S. registered trademark of E.I. DuPont de Nemours and Company.

Designing Interfaces for the ECLIPSE® I/O Bus 014-001856-00

Revision History:

Original Release - January 1990

## **Preface**

The ECLIPSE I/O bus is a characteristic feature of most models in the ECLIPSE® MV/Family of computers.

The input/output subsystem of a computer featuring an ECLIPSE I/O bus consists of an input/output controller (IOC) or equivalent circuitry that controls the input/output bus and the burst multiplexor channel (BMC) controller that controls the BMC bus. In this manual, for the sake of clarity, we refer to the IOC as the input/output bus controller and the BMC controller as the BMC bus controller.

This manual describes how to design input/output (I/O) bus interface circuitry for custom device controllers that connect to the Data General ECLIPSE I/O bus. While little knowledge of the input/output architecture of the system is needed to use a peripheral device sold by Data General Corporation (DGC), the design of an input/output device controller requires a much greater understanding of this architecture. This manual describes the programmed input/output (PIO), data channel (DCH), and burst multiplexor channel (BMC) facilities of the system and describes the structure, functions, signals, and timing characteristics of their buses. The manual also describes the general-purpose interface boards that Data General makes available to simplify the job of designing and building an interface. The reader should have a working knowledge of digital circuits and some experience with digital computers.

## **Organization of This Manual**

The manual is divided into chapters as follows:

Chapter 1 introduces the standard ECLIPSE I/O bus subsystem and describes how it integrates with ECLIPSE MV/Family computers.

Chapter 2 describes the various I/O bus functions and the bus signals that are used for each.

Chapter 3 presents detailed timing characteristics and signal levels for the various I/O bus functions, provides circuit specifications for line drivers and receivers that are to be connected to the I/O bus, and lists suggestions for minimizing electrical noise.

Chapter 4 describes the various BMC bus functions and the bus signals that are used for each.

Chapter 5 presents functional timing characteristics and signal levels for the various BMC bus functions. This chapter also describes how to connect to and terminate the BMC bus.

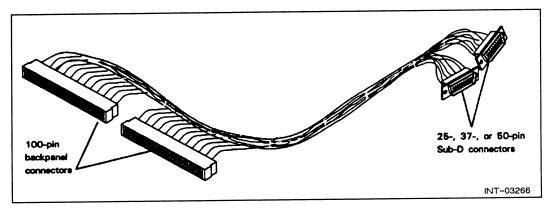

Chapter 6 describes how to connect device controllers in an ECLIPSE MV/Family computer chassis to adapters and devices outside the chassis, how to install internal and external I/O cables, and how to terminate the buses.

Chapter 7 provides information on interfacing boards available from Data General Corporation that will aid the user in constructing custom device controller boards.

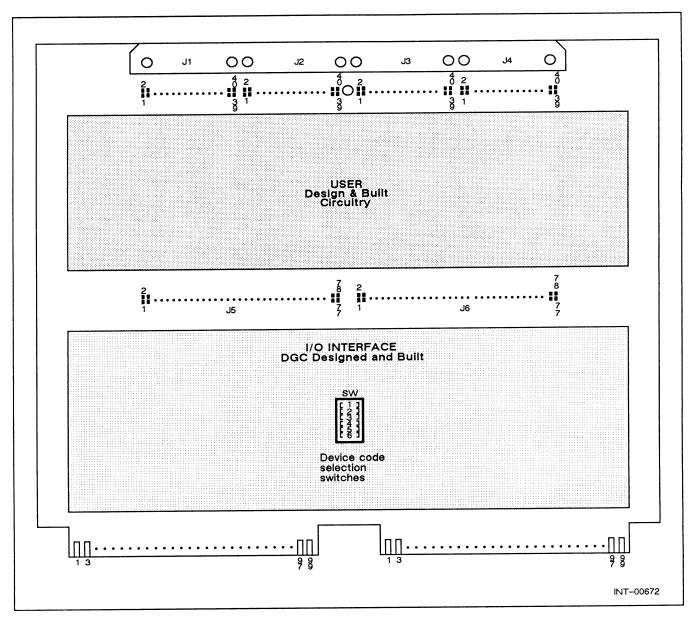

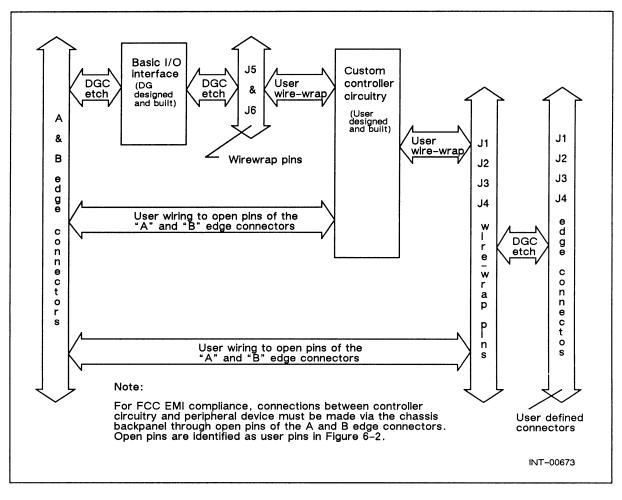

Chapter 8 describes the Model 4040A General Purpose I/O Interface Board, a 15-inch by 15-inch printed circuit board that provides basic I/O bus interface circuitry and an area where a user can construct custom device controller circuitry.

## Reader, Please Note:

The following sections describe conventions in this manual.

#### Backpanel and Backplane

In this manual, *backpanel* and *backplane* are synonymous, both referring to the interconnecting printed-circuit board that passes bus and power signals to other boards. The *backpanel* (*backplane*) contains connectors into which the boards of the system are plugged.

#### **Logic Functions**

Data General logic prints are drawn in close accordance with Mil-Std-806C. With this convention, logical functions are drawn as physically implemented; that is, where discrete gates are used to implement a function, those gates are shown. On the other hand, where a more complex integrated circuit is used (for instance, a multiplexor) it is shown as a rectangular box instead of showing the gates comprising the function.

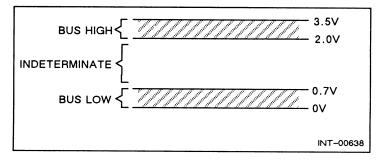

#### Signal Levels

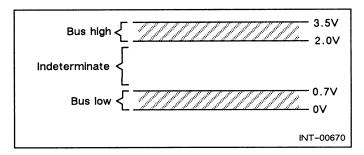

Throughout this manual, we frequently make a distinction between electrical levels and logical values. To minimize confusion, electrical levels are always indicated by an H or L, and logical values by a 1 or 0. As an electrical level, an H indicates that the signal is high (greater then +2.0 volts) and an L indicates that it is low (less than +0.7 volts). An asserted, or true, signal is indicated by a logical 1, and a false signal by a 0.

#### Signal Names

The voltage level at which a signal asserts true is a matter of definition. To distinguish between signals that are asserted high (0 = L, 1 = H) and those that are asserted low (0 = H, 1 = L), we use a naming convention that defines the relationship between the logical value and electrical level of a signal. If a horizontal bar appears over the name, as  $\overline{\text{WRITE}}$ , then that signal is asserted when it is at a low electrical level; conversely, a signal without the bar, WRITE, is asserted when high. To ease the notation in text and in tables, signals that assert low are shown with a  $\hat{}$  preceeding the signal name; for example  $\hat{}$ WRITE asserts low.

The following summary shows the signal notation used within the manual:

| Where Used | Asserts High | Asserts Low |

|------------|--------------|-------------|

| Text       | SIGNALNAME   | ^SIGNALNAME |

| Tables     | SIGNALNAME   | ^SIGNALNAME |

| Figures    | SIGNALNAME   | SIGNALNAME  |

To be expressed, logical functions may often require more than one binary signal. For instance, three lines are required to express an octal digit. Generally, these closely

014-001856

V

related signals are individually named by adding an identifying number to a common label. For instance, suppose that BUS0 through BUS5 are all required to completely specify a function. All or part of such a group of signals is identified by angle brackets around the range of items included; for example, BUS<0-5>. In this case, the range carries the information that there are six BUS lines, BUS0 through BUS5, inclusive.

#### **Related Manuals**

This manual is one of a series of technical manuals available for your ECLIPSE MV/Family computer. These manuals provide detailed technical information on configuring, starting, operating, and programming the system hardware. In general, the manuals are oriented to those with computer hardware background. For designing your software interface (at the assembly language level), you will need the ECLIPSE MV/Family (32-Bit) Systems Principles of Operation manual (014-0001371) as well as the Principles of Operation Supplement for your specific system. For further information on manuals pertaining to your system, contact you Data General sales representative.

## **Contacting Data General**

Data General wants to assist you in any way it can to help you use its products. Please feel free to contact the company as outlined below.

#### **Manuals**

If you require additional manuals, please use the enclosed TIPS order form (United States only) or contact your local Data General sales representative.

If you have comments on this manual, please use the prepaid Comment Form that appears at the back. We want to know what you like and dislike about this manual.

#### **Telephone Assistance**

If you are unable to solve a problem using any manual you received with your system, and you are within the United States or Canada, contact the Data General Service Center by calling 1–800–DG-HELPS for toll-free telephone support. The center will put you in touch with a member of Data General's telephone assistance staff who can answer your questions.

Free telephone assistance is available with your warranty and with most Data General service options. Lines are open from 8:30 a.m. to 8:30 p.m., Eastern Time, Monday through Friday.

For telephone assistance outside the United States or Canada, ask your Data General sales representative for the appropriate telephone number.

|  |  | - |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | - |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | - |

|  |  |   |

|  |  |   |

## **Contents**

#### Chapter 1 – Introduction Device Controller ...... 1–3 Adapter ..... 1–4 Chapter 2 - The I/O Bus I/O Skip .......2-11 Start, Clear, I/O Pulse ......2-11 Busy/Done Network ......2-11 Program Interrupt System ......2–13 Interrupt Request .......2-13 Interrupt Disable ...... 2-14 Interrupt Priority ...... 2-14 Interrupt Acknowledge .......2-16 Data Channel Acknowledge ...... 2-20 Data Channel Map Slot Selection ...... 2-22

#### Chapter 3 - I/O Bus Timing and Electrical Specifications Timing ...... 3-1 Receivers ..... 3-8 Noise ...... 3-8 Chapter 4 - The BMC Bus Transfer Sequence ...... 4-6 Burst Multiplexor Channel Request ..... 4-7 Burst Multiplexor Channel Priority ..... 4-9 Address ..... 4-15 Unmapped/Mapped Transfers ..... 4-17 Output ..... 4–21 Protected Memory Check ...... 4-24 BMC Break Circuitry ...... 4-25 Loading BMC Map from I/O Device Controller ...... 4-26 Chapter 5 – BMC Bus Specifications

VIII 014-001856

#### Chapter 6 - Device Connections and Connectors I/O Bus Connections ...... 6-2 I/O Bus Connections Outside a Chassis . . . . . . . . . . . . . 6-3 Cabling to an Adapter or Device ..... 6-3 Cabling to User-Designed and Built Interfaces . . . . . . . . . . . . . . . . . 6-3 Chapter 7 – Device Controller Boards Chapter 8 - Model 4040A General-Purpose I/O Interface Board Functional Description ...... 8-3 I/O Control Signals ...... 8-4 Busy and Done Flags .......8-4

014-001856 **iX**

# **Tables**

| Table             |                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| 2-1<br>2-2<br>2-3 | I/O Bus Signals       2-4         Test Conditions       2-11         Data Channel Transfer Modes       2-25 |

| 4-1<br>4-2        | BMC Bus Signals                                                                                             |

| 6-1               | General-Purpose Internal Device Cables                                                                      |

| 8-1               | Electrical Characteristics                                                                                  |

| 8-2               | Operating Environmental Specifications                                                                      |

| 8-3               | General Specifications                                                                                      |

| 8-4               | Jumper Connections for Output Register                                                                      |

| 8-5               | Jumper Connections for Input Register 8-14                                                                  |

| 8-6               | I/O Control                                                                                                 |

| 8-7               | Input Data 8–16                                                                                             |

| 8-8               | Output Data                                                                                                 |

| 8-9               | Input Data Register                                                                                         |

| 8-10              | Output Shift/Data Registers 8-18                                                                            |

| 8-11              | Data Channel Control                                                                                        |

| 8-12              | DCH Word Counter 8-19                                                                                       |

| 8-13              | DCH Address Counter 8–19                                                                                    |

| 8-14              | J5 Wire-Wrap Pins 8-20                                                                                      |

| 8-15              | J6 Wire-Wrap Pins                                                                                           |

X 014-001856

# **Figures**

| Figure |                                                                     |

|--------|---------------------------------------------------------------------|

| 1-1    | I/O Bus Interconnection                                             |

| 1-2    | An ECLIPSE Computer System                                          |

|        | •                                                                   |

| 2-1    | The I/O Bus                                                         |

| 2-2    | Single Device Code Selection Network                                |

| 2-3    | Multiple Device Code Selection Network                              |

| 2-4    | Data In Sequence 2–9                                                |

| 2-5    | Data Out Sequence                                                   |

| 2-6    | Busy/Done Sequencing                                                |

| 2-7    | Typical Busy/Done Network                                           |

| 2-8    | Typical Priority Mask Bit Circuit                                   |

| 2-9    | Typical Interrupt Priority Chain                                    |

| 2-10   | Interrupt Priority Chain                                            |

| 2-11   | Typical Interrupt Control Circuit                                   |

| 2-12   | Typical Data Channel Request Circuit                                |

| 2-13   | Typical Data Channel Sequence                                       |

| 2-14   | Typical Data Channel Priority Circuit                               |

| 2-15   | Data Channel Priority Chain2-19                                     |

| 2-16   | Typical Data Channel Select Circuit                                 |

| 2-17   | Data Channel Sequencing                                             |

| 2-18   | Typical Data Channel Control Circuit (Complete)                     |

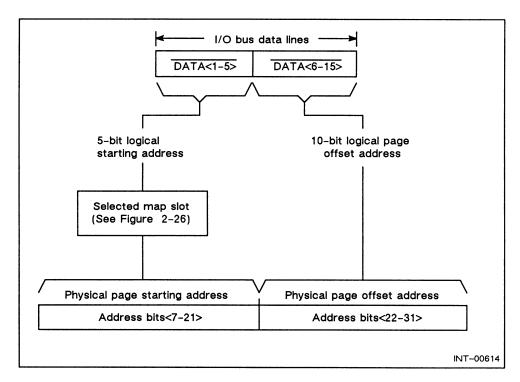

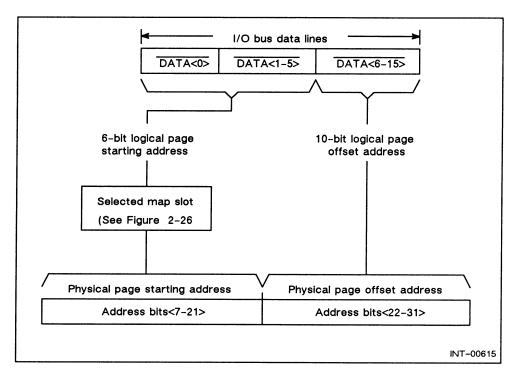

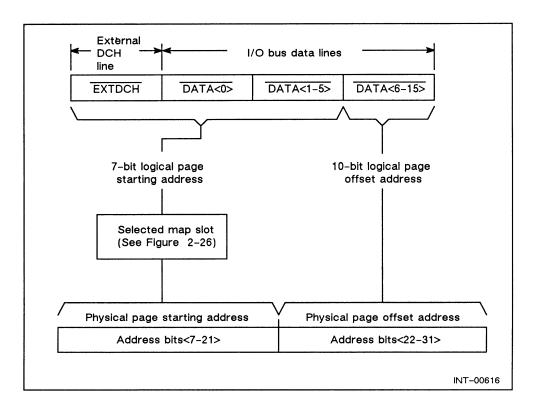

| 2-19   | Data Channel I/O Controller Memory Addressing Schemes 2-22          |

| 2-20   | 19-Bit Logical-to-Physical Address Translation                      |

| 2-21   | 15-Bit Logical-to-Physical Address Translation                      |

| 2-22   | 16-Bit Logical-to-Physical Address Translation                      |

| 2-23   | 12-Bit Logical-to-Physical Address Translation                      |

| 2-24   | Data Channel Input Sequence                                         |

| 2-25   | Data Channel Output Sequence                                        |

| 2-26   | Data Channel Memory Map Register Locations                          |

| 2-27   | Address Word Format for Data Channel Map Upstream Loading 2-28      |

| 2-28   | Input/Output Map Even-Numbered Register Format                      |

|        | (High-Order Word)                                                   |

| 2-29   | Input/Output Map Odd-Numbered Register Format (Low-Order Word) 2-29 |

| 3-1    | Programmed I/O Input Without Start, Clear, or I/O Pulse 3-1         |

| 3-2    | Programmed I/O Input with Start, Clear, or I/O Pulse                |

| 3-3    | Programmed I/O Output Without Start, Clear, or I/O Pulse 3-2        |

| 3-4    | Programmed I/O Output with Start, Clear, or I/O Pulse               |

| 3-5    | Programmed I/O No Data Transfer with Start, Clear, or I/O Pulse 3-3 |

| 3-6    | Mask Out                                                            |

|        |                                                                     |

014-001856 Xİ

| 3-7  | Skip Test                                                     |        |

|------|---------------------------------------------------------------|--------|

| 3-8  | Program Interrupt                                             | 3–3    |

| 3-9  | Interrupt Priority Chain                                      | 3–4    |

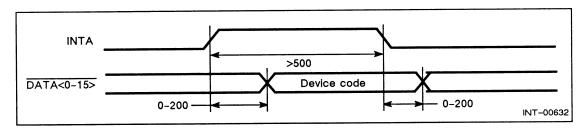

| 3-10 | Interrupt Acknowledge                                         | 3–4    |

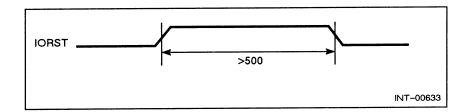

| 3-11 | I/O Reset                                                     | 3–4    |

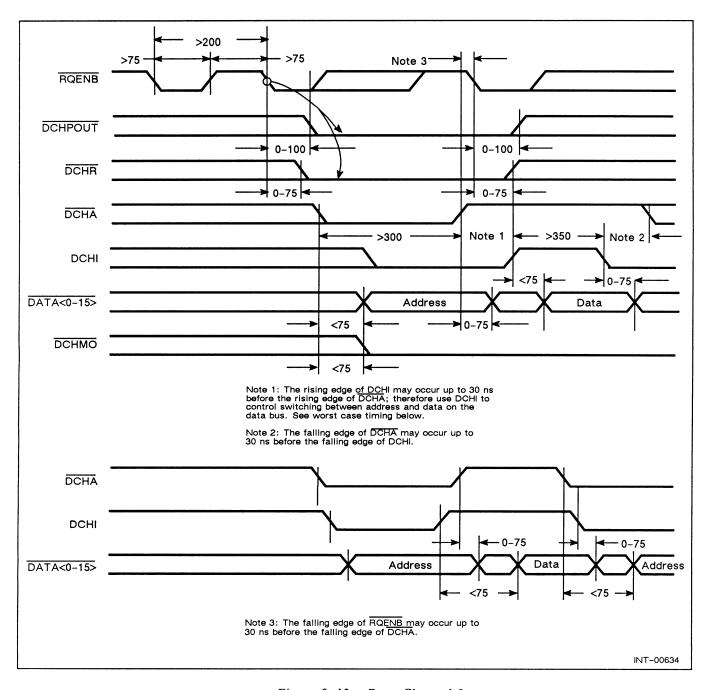

| 3-12 | Data Channel Input                                            |        |

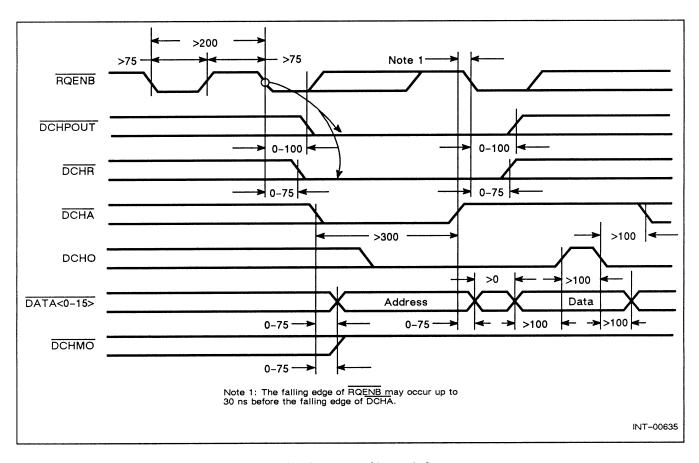

| 3-13 | Data Channel Output                                           | 3-6    |

| 3-14 | Data Channel Priority Chain                                   | 3–6    |

| 3-15 | Data Channel Priority to Acknowledge Delay                    | 3-7    |

| 3-16 | Bus Electrical Levels                                         | 3–7    |

| 3-17 | Typical Line Driver                                           | 3–8    |

| 3-18 | Bus Receiver                                                  | 3–9    |

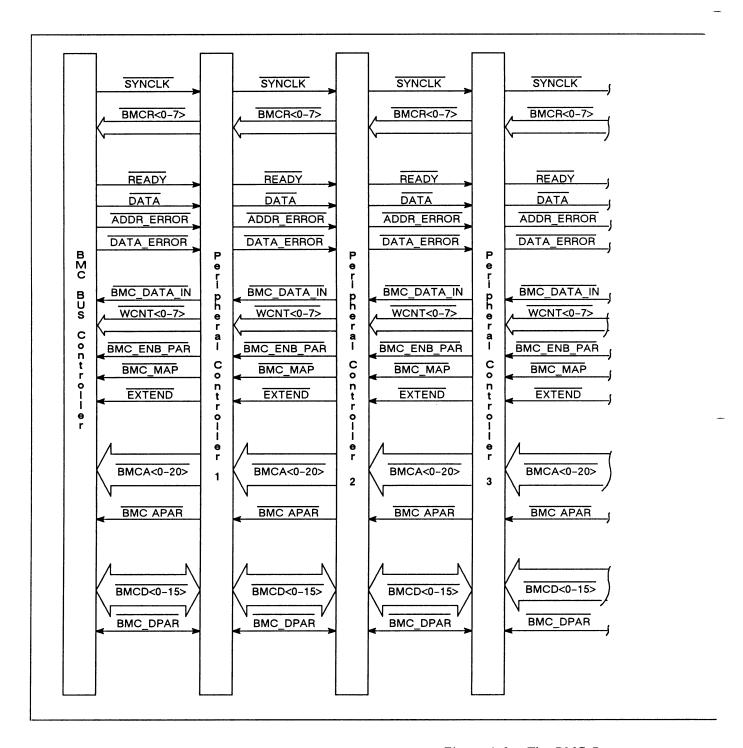

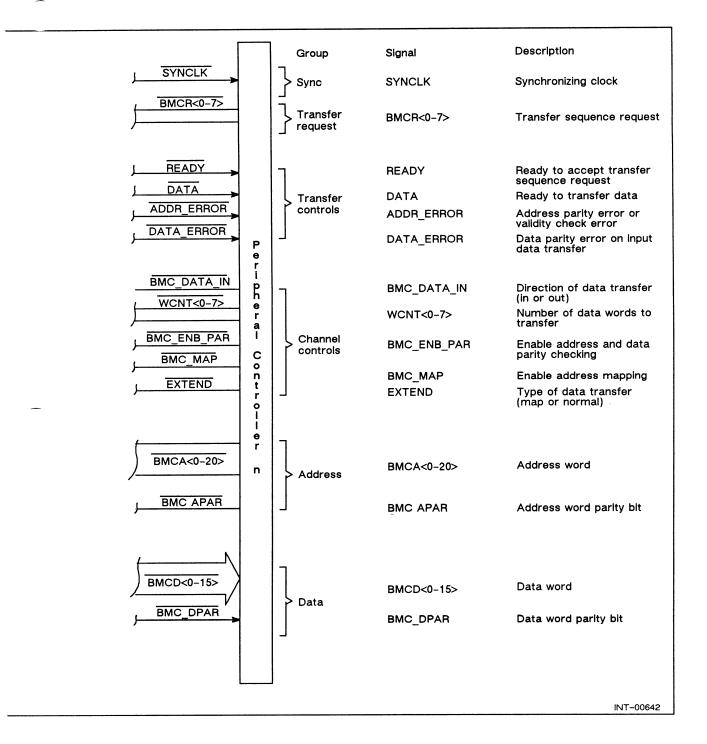

| 4-1  | The BMC Bus                                                   |        |

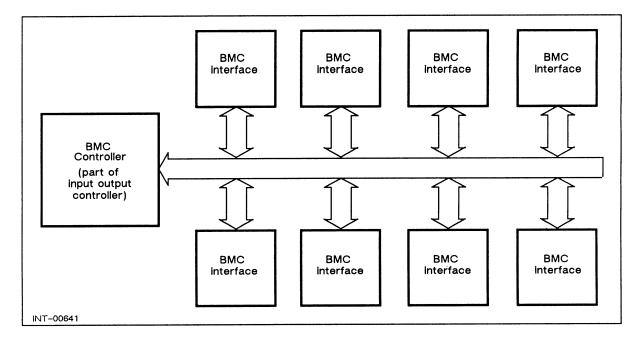

| 4-2  | BMC Bus Interconnection                                       |        |

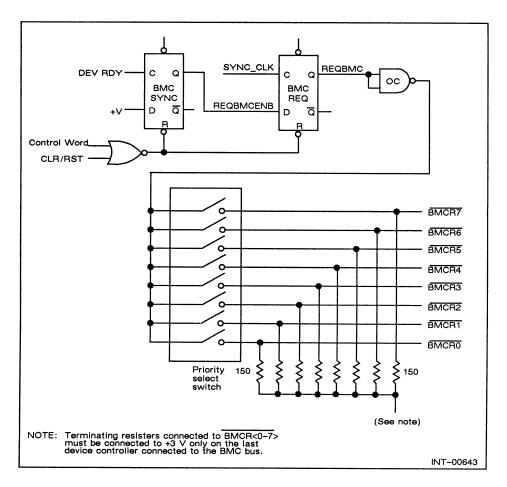

| 4-3  | Typical BMC Request Circuit                                   |        |

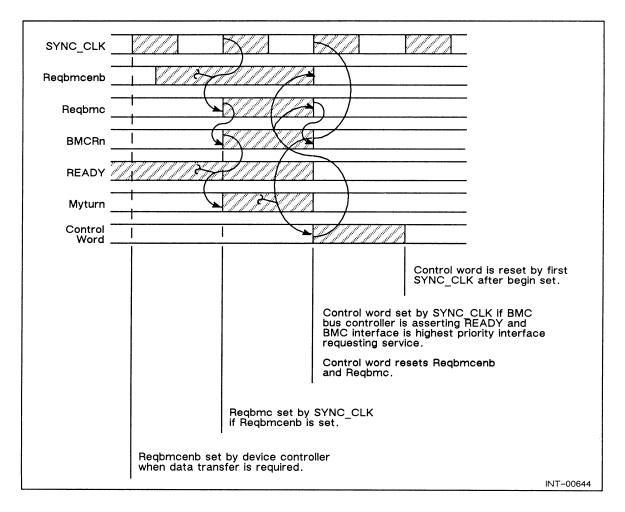

| 4-4  | Typical BMC Request Sequence (BMC Bus Controller Ready)       |        |

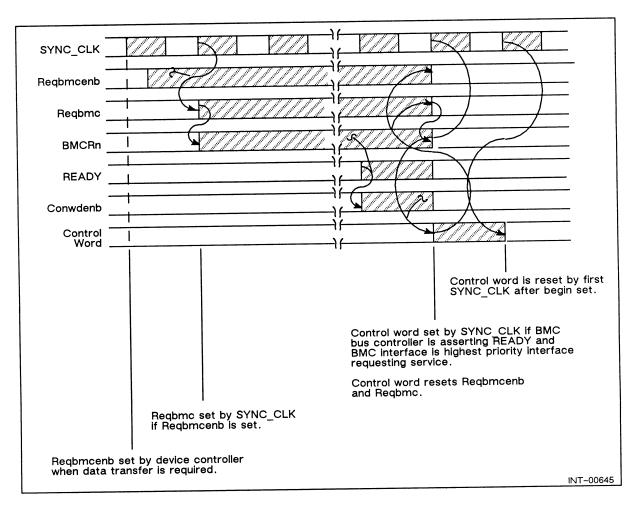

| 4-5  | Typical BMC Request Sequence (BMC Bus Controller Not Ready)   |        |

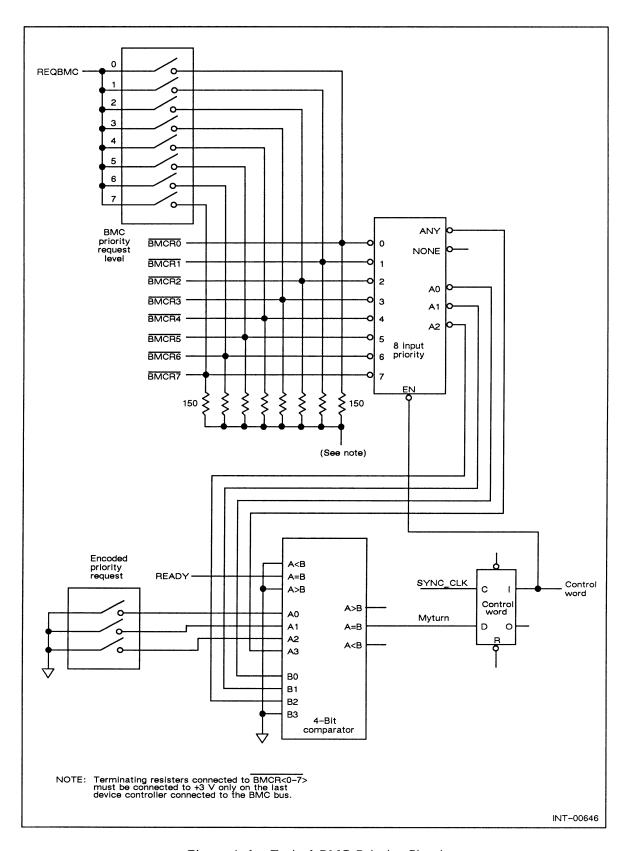

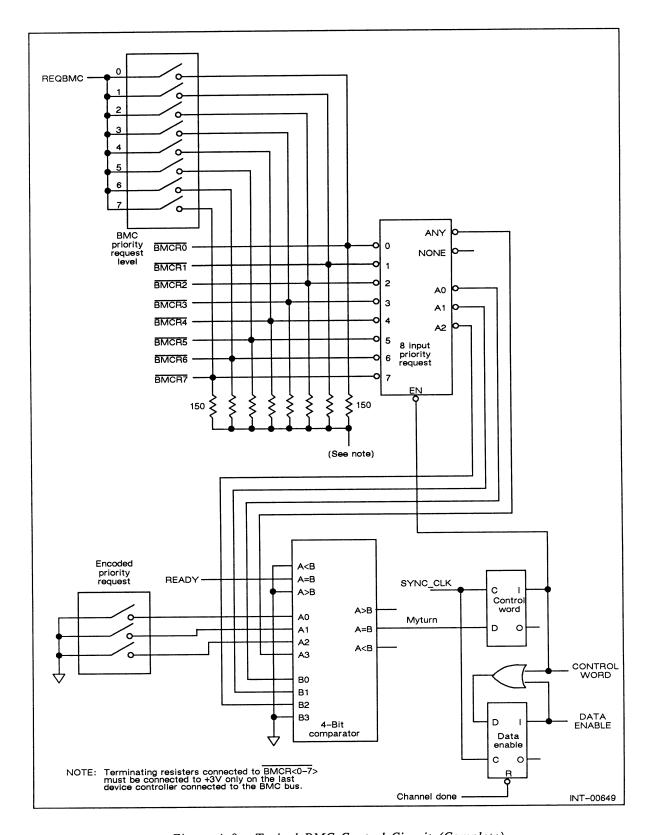

| 4-6  | Typical BMC Priority Circuit                                  |        |

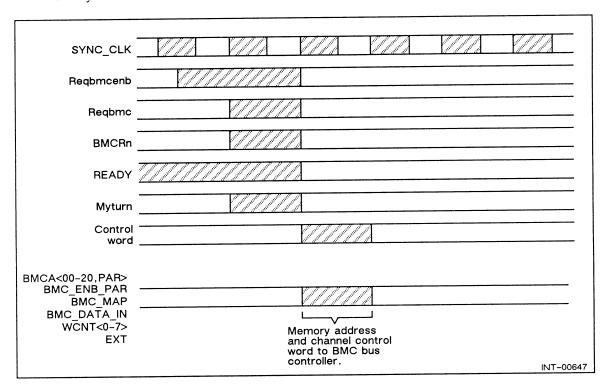

| 4-7  | Typical BMC Memory Address and Channel Control Word Sequence  | . 4–12 |

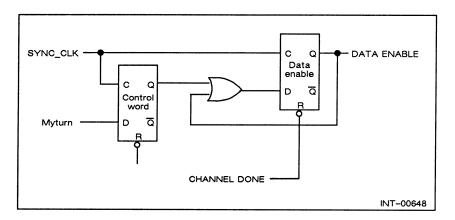

| 4-8  | Typical BMC Select Circuit                                    |        |

| 4-9  | Typical BMC Control Circuit (Complete)                        | . 4–14 |

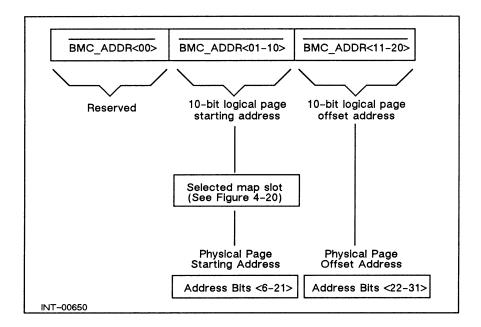

| 4-10 | Logical-to-Physical Address Translation                       |        |

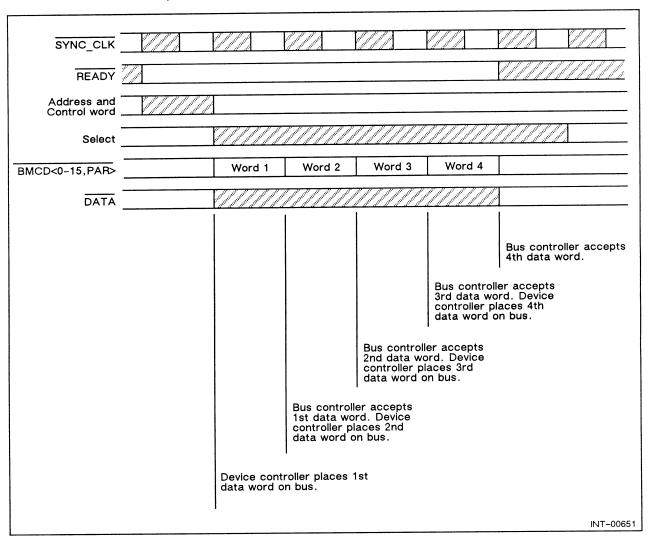

| 4-11 | BMC Data Input Sequence                                       |        |

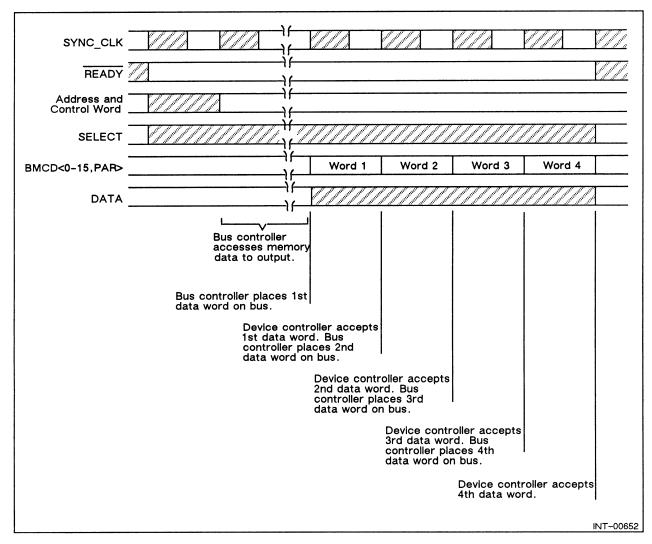

| 4-12 | BMC Data Output Sequence                                      | . 4-21 |

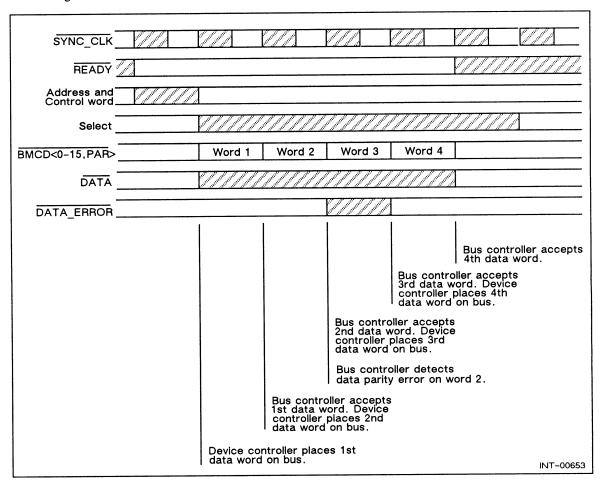

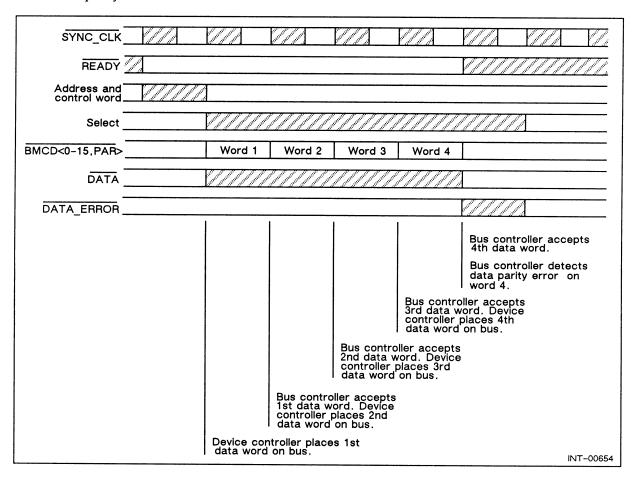

| 4-13 | Data Parity Error Detected on Input Transfer                  |        |

|      | (Not on Last Word)                                            | . 4–22 |

| 4-14 | Data Parity Error Detected on Last Input Word Transferred     | . 4–23 |

| 4-15 | Protected Memory Error Detected on Input Data Transfer        | 4 0 4  |

|      | (Not on Last Word)                                            | . 4-24 |

| 4–16 | Protected Memory Error Detected Following Last Input Word     | 4 05   |

|      | Transferred                                                   | . 4-25 |

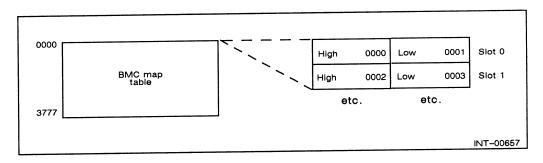

| 4-17 | BMC Memory Map Register Locations                             |        |

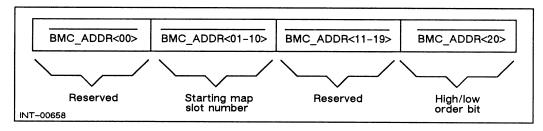

| 4-18 | Address Word Format for BMC Map Upstream Loading              |        |

| 4-19 | BMC Map Even-Numbered Register Format (High-Order Word)       |        |

| 4–20 | BMC Map Odd-Numbered Register Format (Low-Order Word)         | . 4–28 |

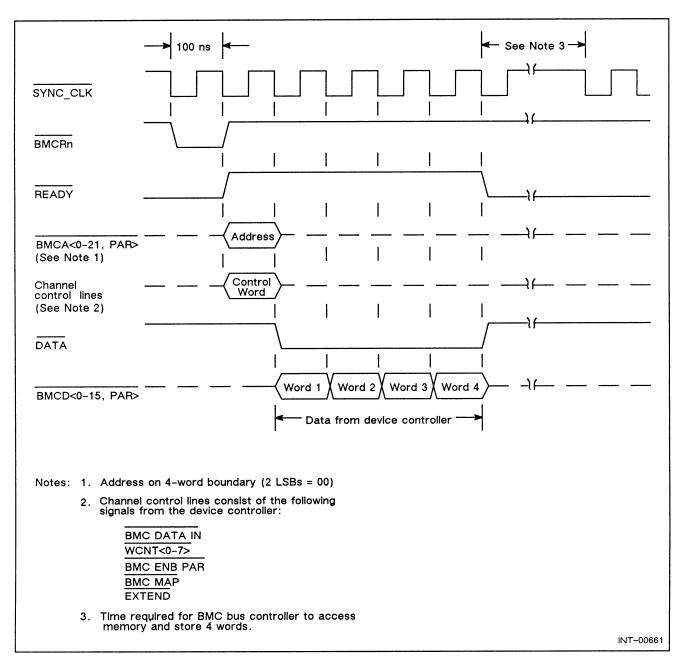

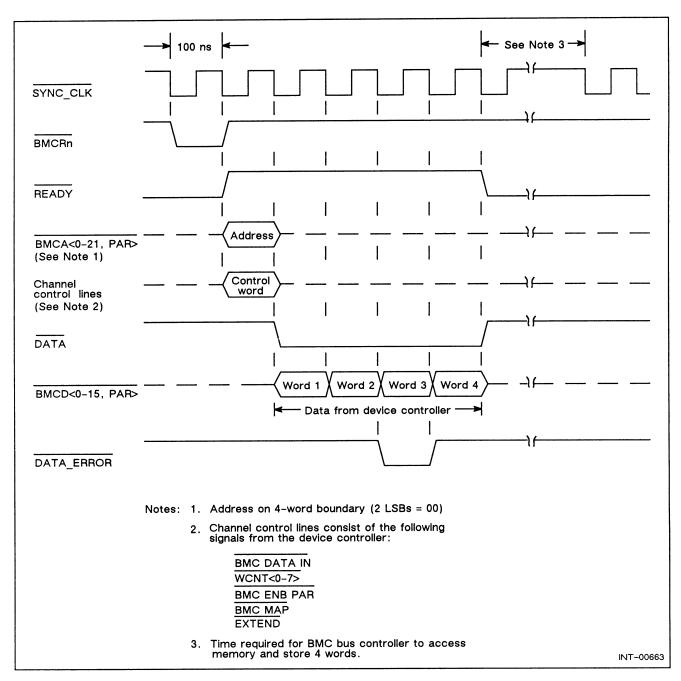

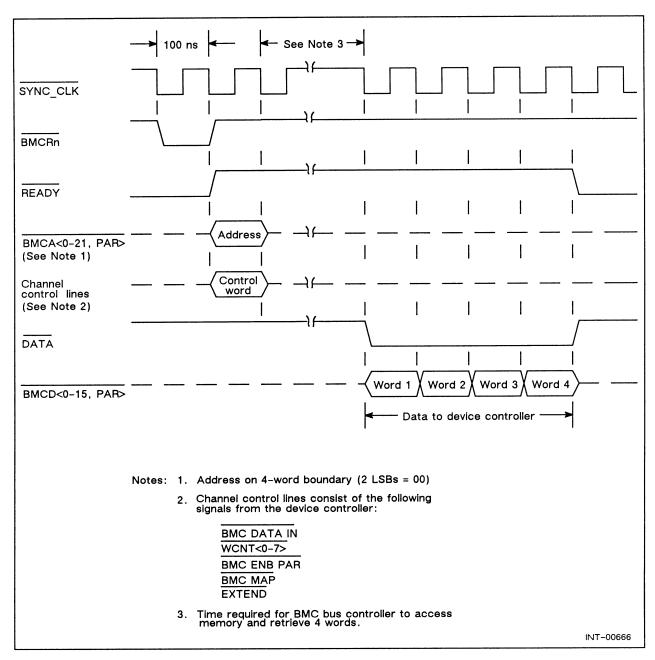

| 5-1  | Data Input (1 Request, 4 Words, No Errors)                    |        |

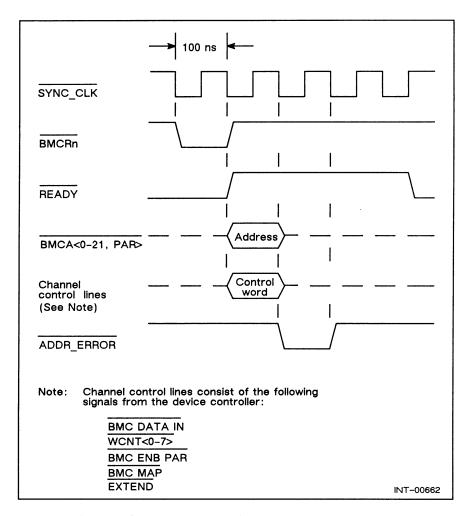

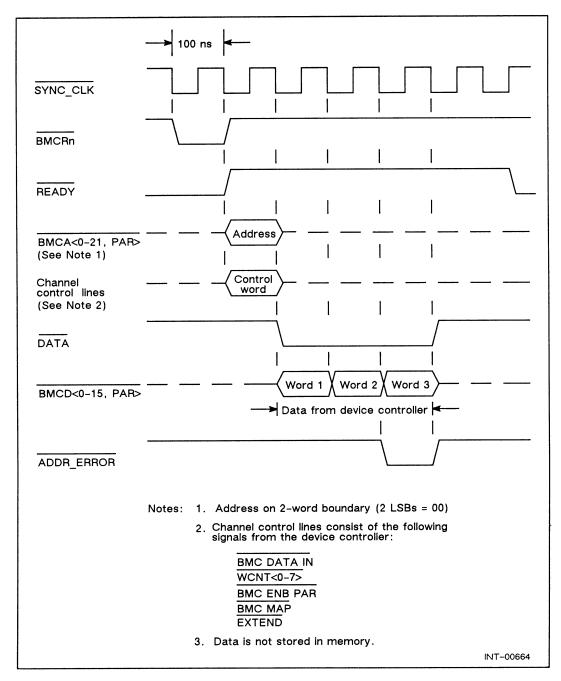

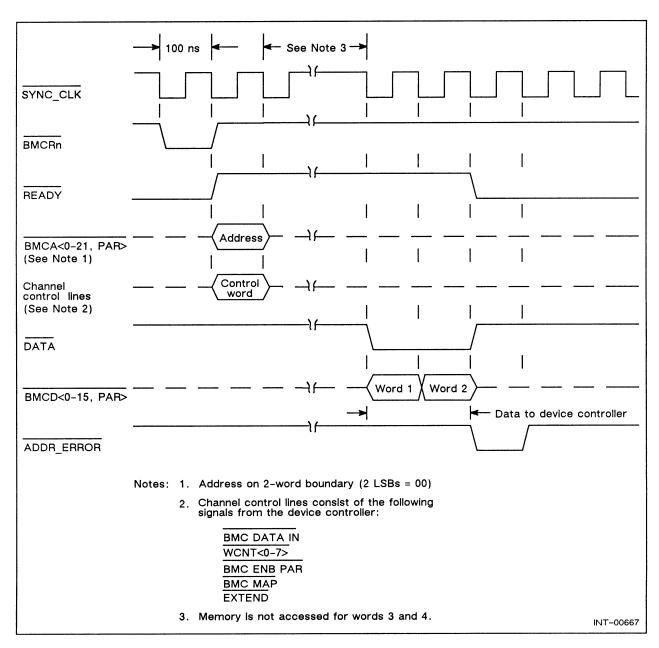

| 5-2  | Address Parity Error (Input or Output)                        |        |

| 5-3  | Data Input (1 Request, 4 Words, Data Parity Error)            |        |

| 5-4  | Data Input (1 Request, 4 Words, Protected Memory Error)       |        |

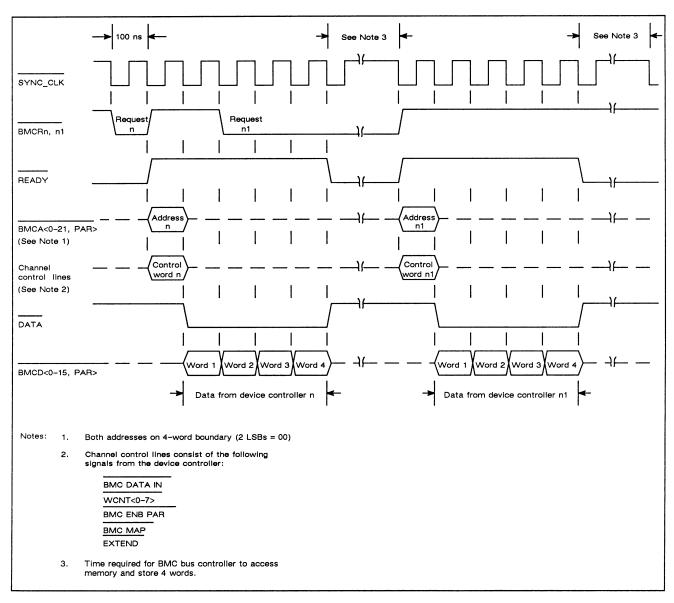

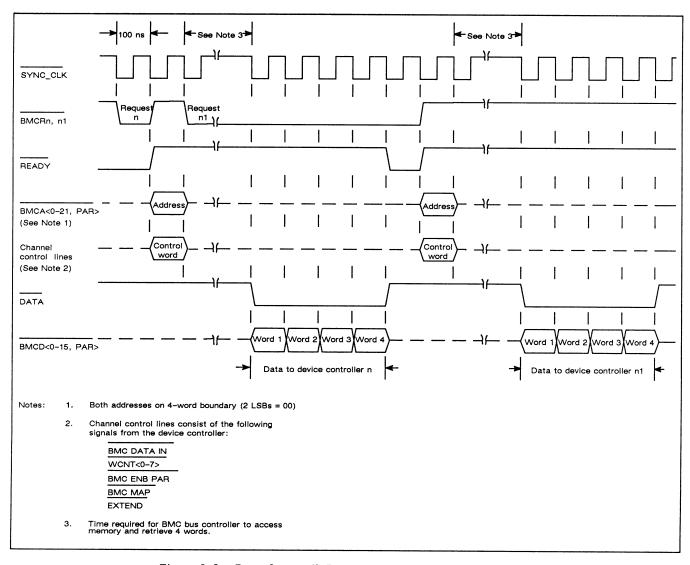

| 5-5  | Data Input (2 Requests, 4 Words Each, No Errors)              |        |

| 5-6  | Data Output (1 Request, 4 Words, No Errors)                   |        |

| 5-7  | Data Output (1 Request, 4 Words, Protected Memory Error)      |        |

| 5-8  | Data Output (2 Requests, 4 Words Each, No Errors)             |        |

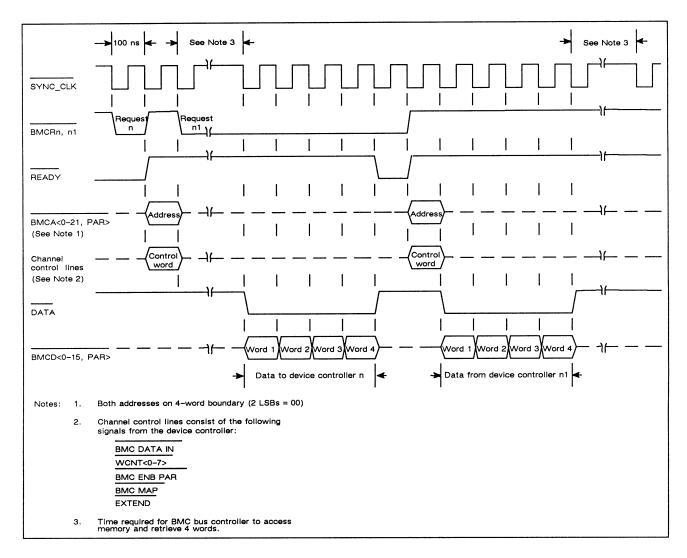

| 5-9  | Two Requests (1st Output; 2nd Input, 4 Words Each, No Errors) |        |

| 5-10 | Bus Electrical Levels                                         |        |

| 5-11 | BMC Bus Connector Pin Layout                                  | . 5-13 |

**Xİİ** 014-001856

| 6-1 | Typical Internal Device Cable6–2                                   |

|-----|--------------------------------------------------------------------|

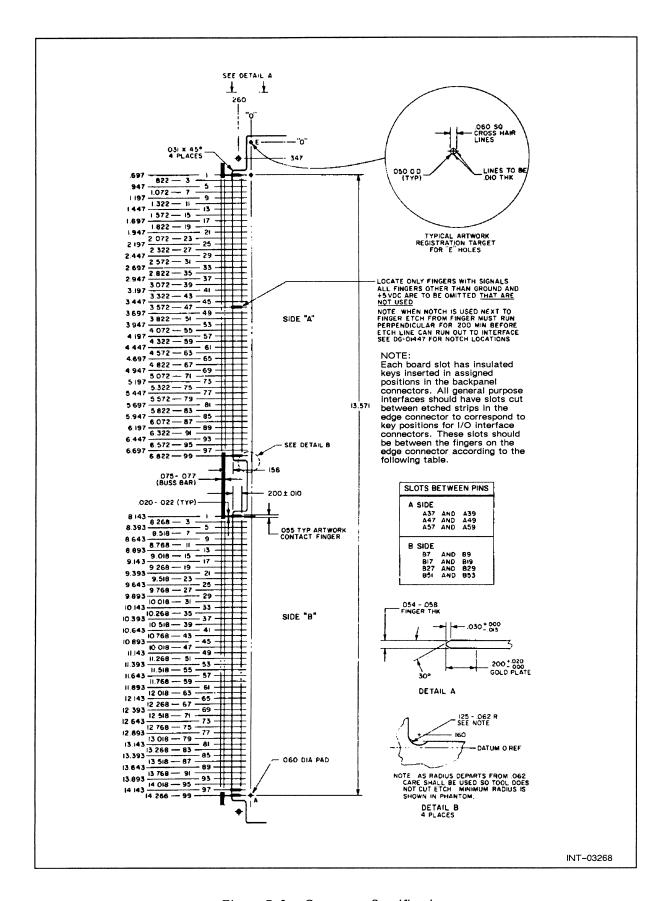

| 6-2 | Input/Output Backpanel Connector Layout (Viewed from Pin Side) 6-4 |

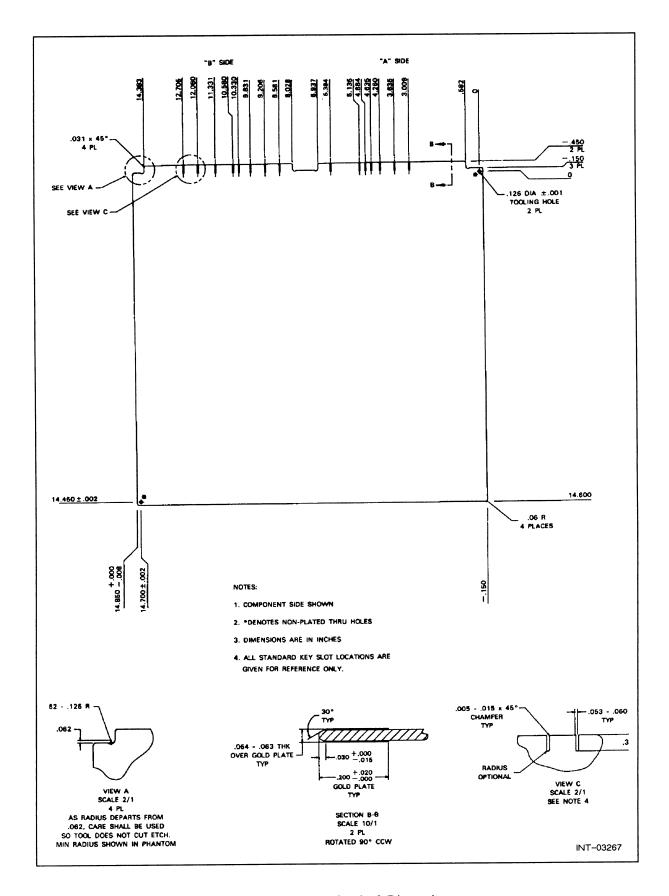

| 7-1 | Mechanical Dimensions                                              |

| 7-2 | Connector Specifications                                           |

| 7-3 | 1000 Series Wiring Board 7-6                                       |

| 7-4 | 1000 Series Module Board Hole Pattern                              |

| 7–5 | 1020 Series Wiring Board                                           |

| 8-1 | Model 4040A Printed Circuit Board Layout 8-2                       |

| 8-2 | Model 4040A Printed Circuit Board Features 8-3                     |

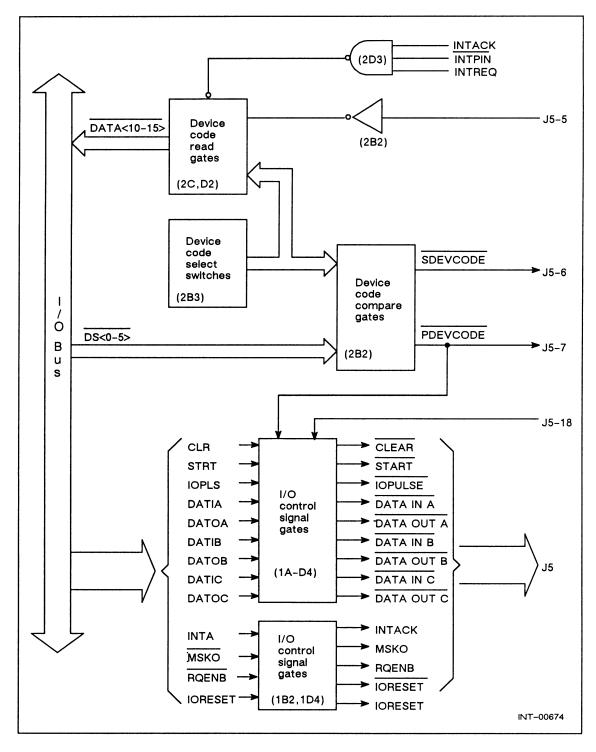

| 8-3 | Device Selection and I/O Control Signals 8-5                       |

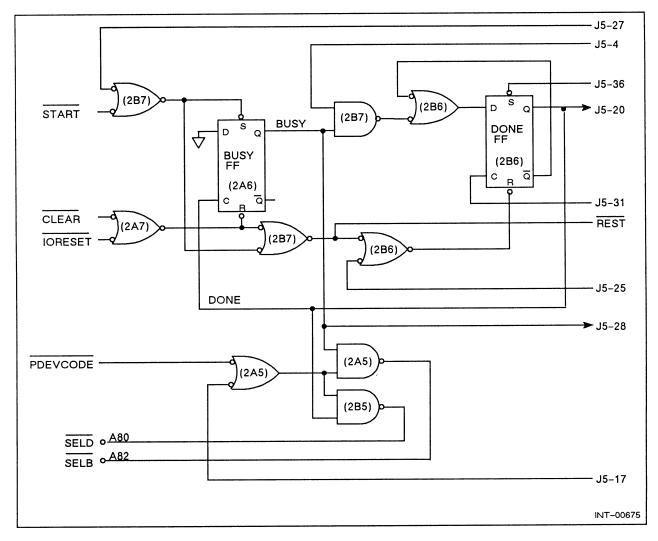

| 8-4 | Model 4040A Busy and Done Circuitry8-6                             |

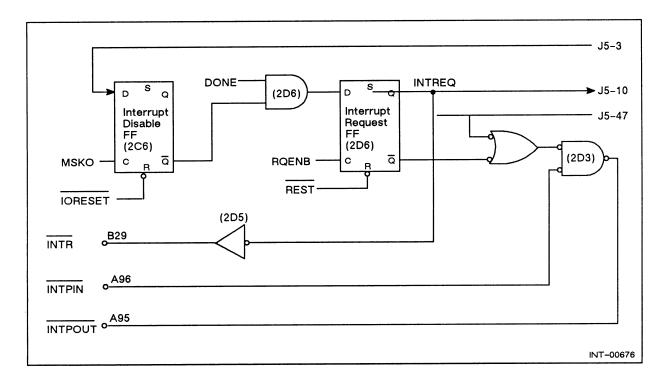

| 8-5 | Model 4040A Interrupt Control Circuitry 8-7                        |

| 8-6 | Model 4040A Data Handling Circuitry8-8                             |

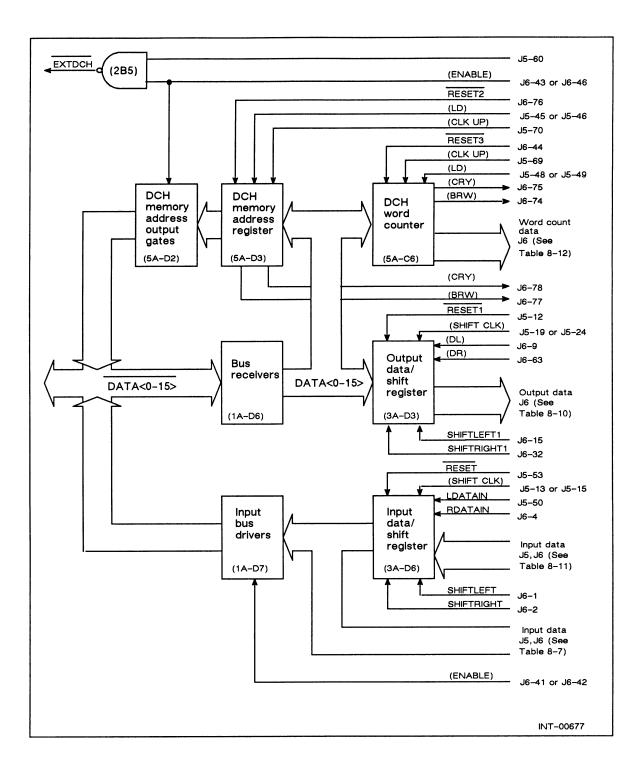

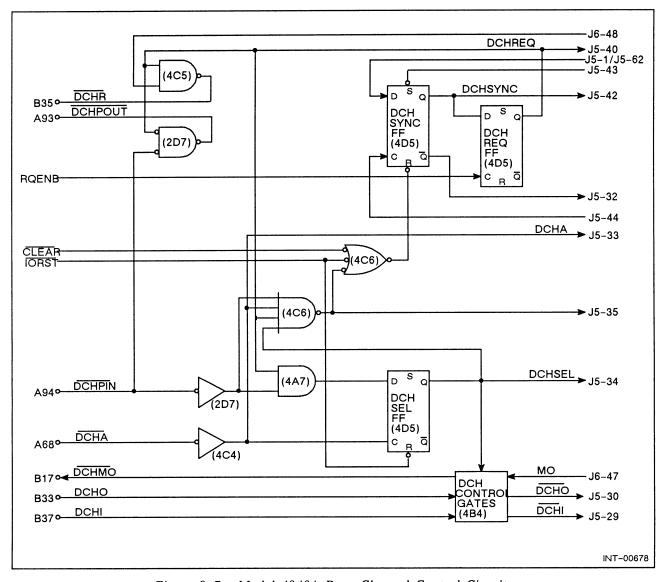

| 8-7 | Model 4040A Data Channel Control Circuitry 8-9                     |

| 8-8 | Switch Settings                                                    |

014-001856 **Xiii**

|  |  | -     |

|--|--|-------|

|  |  |       |

|  |  |       |

|  |  |       |

|  |  |       |

|  |  |       |

|  |  | and . |

|  |  |       |

# Chapter 1 Introduction

This chapter introduces the standard ECLIPSE I/O bus subsystem and describes how it integrates with ECLIPSE® MV/Family computers.

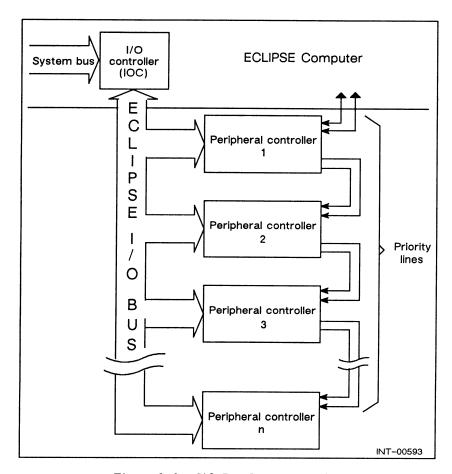

As shown in Figure 1–1, the ECLIPSE I/O bus subsystem connects peripheral devices, via their controllers, with the host computer. The ECLIPSPE I/O bus subsystem consists of two buses: a data channel and input/output bus (referred to as the I/O bus), and a burst multiplexor channel (BMC) bus. Each of these buses consists of several conductors used for transmitting control and information signals between the computer and the device controllers. The I/O bus is shared by all the device controllers as well as by the computer, while the BMC bus is shared only by the device controllers that incorporate the BMC facility and the computer. Since these buses are shared by both the computer and the peripherals, they are, by necessity, half-duplex buses; that is, only one operation can occur at any one time on a particular bus. However, both buses may have operations occurring simultaneously, independent of each other.

Figure 1-1 I/O Bus Interconnection

The BMC bus is the preferred I/O link for mass storage devices. Since the channel has to be activated only once and a memory address has to be supplied only once for each burst of words transferred, block transfers over the BMC can occur at much higher rates than those under I/O.

The direction of all information transfers on the buses is relative to the computer. *Output* always refers to information moving from the computer to a device controller; *input* always refers to information moving from a device controller to the computer.

## Integration with System

A basic ECLIPSE computer system using the ECLIPSE I/O bus consists of a computer, its peripheral devices, and an I/O bus that connects the peripheral devices with the computer. Figure 1–2 shows these parts of the system as well as other components mentioned in the following paragraphs and it shows their interconnections.

Figure 1-2 An ECLIPSE Computer System

#### Computer

A basic ECLIPSE computer consists of a central processing unit (CPU), a memory, and an IOC. The IOC incorporates the two types of I/O bus controllers: an I/O bus controller and a BMC bus controller. The computer may include other elements, such as a hardware floating-point unit (FPU), but Figure 1-2 shows the simplest implementation.

1–2

#### Input/Output

Input/output is the process of moving information in a computer system between the computer and peripheral devices such as line printers, terminals, and mass storage devices (tape and disk units). Some devices, such as line printers, transfer information out of the system. Some devices, such as terminals, transfer information both into and out of the system. Others, such as mass storage devices, not only transfer information into or out of the system, but also store information within the system. Devices, therefore, serve two main purposes: they provide the computer system with a means of communicating with its surroundings, and they supplement memory with secondary information storage capacity.

#### Input/Output Controller (IOC)

The IOC generates the ECLIPSE I/O bus and acts as an intermediary between I/O devices on the bus and the rest of the system. It communicates with the CPU and memory via the internal system buses and with peripheral devices via the ECLIPSE I/O bus. To the operating system, the IOC appears as an I/O channel, supporting data channel and burst multiplexor channel (BMC) devices with internal and external bus protocol transformations. It maintains maps that change data channel and BMC addresses to physical memory addresses. Although the IOC allows intelligent device controllers to load their own memory maps, it also maintains protection bits that prevent devices from gaining access to protected memory areas. Several IOCs can be present in some ECLIPSE MV/Family systems, each generating an ECLIPSE I/O bus. Other implementations of ECLIPSE MV/Familiy systems may have only one IOC and thus only one ECLIPSE I/O bus. When more than one ECLIPSE I/O bus is present, they are identical.

#### **Peripherals**

A *peripheral* generally consists of several units: a device or devices; a device controller; and, sometimes, an adapter.

#### **Devices**

A device is a unit that reads, writes, stores, or processes information. Devices include disk drives, magnetic tape transports, and display and hardcopy terminals. For example, a terminal's keyboard reads information; a plotter writes information; a disk drive and magnetic tape transport stores information; and an analog-to-digital (A/D) converter processes information.

#### **Device Controller**

A device controller is the interface between the computer and the device, interpreting commands from the computer to the device and passing information between them. Thus, a moving-head disk controller can translate the track address received from the computer into positional commands for the disk drive's access mechanism. Once the access mechanism positions the read/write heads, the disk controller translates the data words it receives from the computer into the sequence of serial bits required by the disk drive write circuitry. Likewise the disk controller translates the sequence of serial bits it receives from the disk drive read circuitry into the data words required by the computer.

#### **Adapter**

An *adapter* is an additional unit required by some peripherals to complete the communications link between the device and the device controller. An example of an adapter is a modulator-demodulator (modem) connected between a communications controller and a remote terminal device.

End of Chapter

1–4

# Chapter 2 The I/O Bus

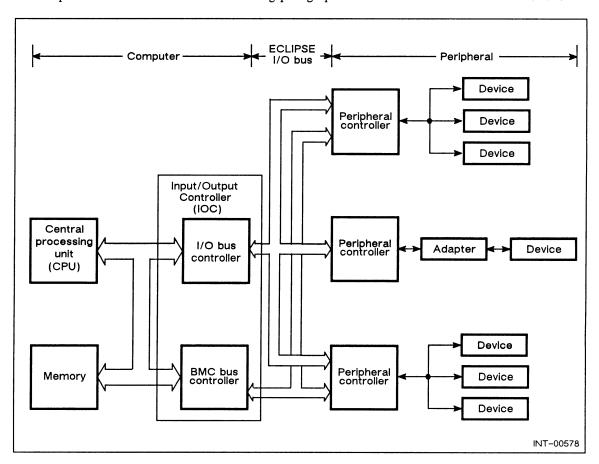

The data channel and input/output (I/O) bus is a single bus connecting an I/O controller (IOC) to the device controllers for peripheral devices (see Chapter 1). The I/O bus handles both the programmed input/output and data channel operations of the computer system.

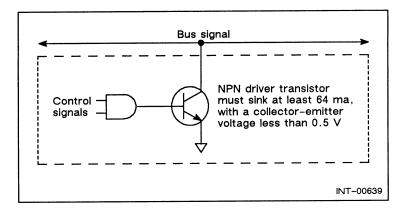

Data and addresses are transferred on the bus along 16 parallel, bidirectional data lines. Data and address transfers are synchronous; no handshaking occurs between the interface and the I/O bus controller. Control signals are carried along dedicated, unidirectional control lines that specify a unique function to be performed. In addition to specifying a unique function, each control signal generated by the I/O bus controller provides all timing necessary to perform that function. The data channel and program interrupt facilities each uses its own single request and single priority lines. The two request lines run in parallel to all peripheral interfaces so that an interface requiring either data channel or program interrupt service need only assert the appropriate line and wait for the response. The serial priority lines are independent and are chained from interface to interface so that priority for service is granted to the interface closest on the chain to the I/O bus controller. The I/O bus is transistor–transistor logic (TTL) compatible.

The I/O bus signals are carried by etching contained on the chassis' printed circuit backpanel (backplane). When there are less than three input/output controllers in a system, internal cabling carries the I/O bus signals between the groups of I/O printed circuit board slots designated for each I/O port. In addition, the ECLIPSE I/O bus(es) can be connected to an expansion chassis when system configurations require expansion. A bus repeater printed circuit board is required when connecting the I/O bus(es) to an expansion chassis. The I/O bus signals are terminated by resistor networks that are solder–mounted on the chassis' backpanel.

## I/O Bus Signals

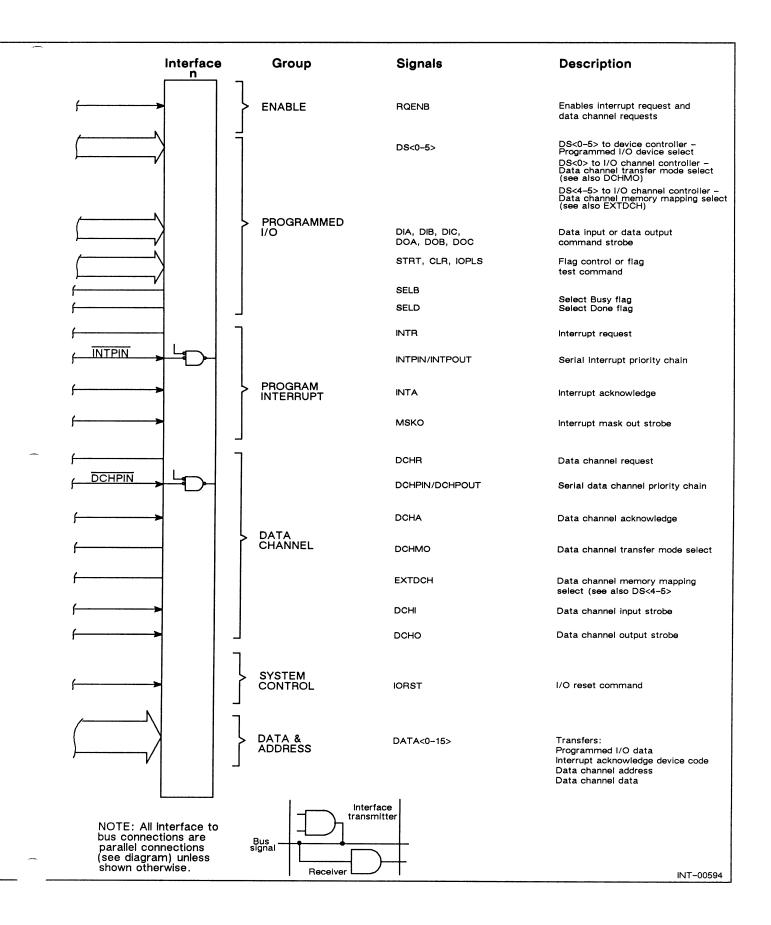

The I/O bus comprises 48 signals that can be divided functionally into 5 groups. Figure 2–1 shows the I/O bus signals in their respective groups and Table 2–1 provides a brief description of each signal's function. (Refer to "Reader, Please Note" in the Preface for signal level and signal name descriptions.) Specific timing information for the I/O bus signals is shown in Chapter 3. Note that, with the exception of the two priority lines, all I/O bus signal lines run in parallel to the I/O bus controller and all device controllers connected to the bus.

Figure 2-1 The I/O bus

Table 2-1 I/O Bus Signals

| Signal      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ^DATA<0-15> | Data. All data and addresses, for both programmed I/O and data channel, are transferred between the I/O bus controller and device controllers connected to the I/O bus via these 16 bidirectional lines. The Interrupt Disable mask and Interrupt Acknowledge information are also carried on these lines.                                                                                                                                                                |

| Programmed  | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

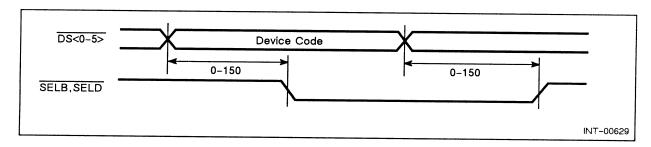

| ^DS<0-5>    | Device Select. These lines, when asserted by the I/O bus controller, carry the low-order 6 bits of an I/O instruction; that is, the device code. Only the device controller whose device code corresponds to that carried on these lines should respond to control signals generated on the I/O bus.                                                                                                                                                                      |

|             | ^DS<0> is bidirectional and can be asserted by device controllers to select data channel transfer mode. (See the ^DCHMO entry later in this table.)                                                                                                                                                                                                                                                                                                                       |

|             | ^DS<4-5> are bidirectional and can be used by device controllers for data channel map selection during data transfers (see section "Data Channel Map Slot Selection").  ^DS<4-5> can also be used when loading data channel map slots from the device controller. (See the ^EXTDCH entry later in this table.)                                                                                                                                                            |

| DATIA       | Data In A. This signal line is asserted by the I/O bus controller during the execution of a Data In A (DIA) instruction. Should cause the device controller selected by ^DS<0-5> to place the contents of its A input buffer on ^DATA<0-15>.                                                                                                                                                                                                                              |

| DATIB       | Data In B. This signal line is asserted by the I/O bus controller during the execution of a Data In B (DIB) instruction. Should cause the device controller selected by ^DS<0-5> to place the contents of its B input buffer on ^DATA<0-15>.                                                                                                                                                                                                                              |

| DATIC       | Data in C. This signal line is asserted by the I/O bus controller during the execution of a Data In C (DIC) instruction. Should cause the device controller selected by ^DS<0-5> to place the contents of its C input buffer on ^DATA<0-15>.                                                                                                                                                                                                                              |

| DATOA       | Data Out A. This signal line is asserted by the I/O bus controller during the execution of a Data Out A (DOA) instruction, after the I/O bus controller has placed the contents of the specified CPU accumulator on ^DATA<0-15>. Should cause the device controller selected by ^DS<0-5> to load its A output buffer with the data on ^DATA<0-15>.                                                                                                                        |

| DATOB       | Data Out B. This signal line is asserted by the I/O bus controller during the execution of a Data Out B (DOB) instruction, after the I/O bus controller has placed the contents of the specified CPU accumulator on ^DATA<0-15>. Should cause the device controller selected by ^DS<0-5> to load its B output buffer with the data on ^DATA<0-15>.                                                                                                                        |

| DATOC       | Data Out C. This signal line is asserted by the I/O bus controller during the execution of a Data Out C (DOC) instruction, after the I/O bus controller has placed the contents of the specified CPU accumulator on ^DATA<0-15>. Should cause the device controller selected by ^DS<0-5> to load its C output buffer with the data on ^DATA<0-15>.                                                                                                                        |

| STRT        | Start. This signal line is asserted by the I/O bus controller during the execution of any I/O instruction (except an I/O Skip instruction) in which bits 8 and 9 = 01 (that is, any I/O instruction in which the $Start$ ( $S$ ) flag control function is specified). Asserted after the data transfer has occurred during DIA, DIB, DIC, DOA, DOB, DOC instructions. Usually used to initiate peripheral operation by setting the Busy flag to 1 and the Done flag to 0. |

| CLR         | Clear. This signal line is asserted by the I/O bus controller during the execution of any I/O instruction (except an $I/O$ Skip instruction) in which bits 8 and 9 = 10 (that is, any I/O instruction in which the Clear (C) flag control function is specified). Asserted after the data transfer has occurred during DIA, DIB, DIC, DOA, DOB, DOC instructions. Usually used to terminate peripheral operation by setting the Busy and Done flags to 0.                 |

(continued)

Table 2-1 I/O Bus Signals

| Signal  | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOPLS   | I/O Pulse. This signal line is asserted by the I/O bus controller during the execution of any I/O instruction (except an I/O Skip instruction) in which bits 8 and 9 = 11 (that is, any I/O instruction in which the Pulse (P) flag control function is specified). Asserted after the data transfer has occurred during DIA, DIB, DIC, DOA, DOB, DOC instructions. Usually used to initiate special peripheral operations. |

| ^SELB   | Selected Busy. This signal line is conditioned by the device controller, selected by the device select lines, to specify the state of the controller's Busy flag. Asserted low if the controller's Busy flag is set to 1.                                                                                                                                                                                                   |

| ^SELD   | Selected Done. This signal line conditioned by the device controller, selected by the device select lines, to specify the state of the controller's Busy flag. Asserted low if the controller's Done flag is set to 1.                                                                                                                                                                                                      |

| Progran | n Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ^INTR   | Interrupt Request. This signal line is asserted low by a device controller to request program interrupt service.                                                                                                                                                                                                                                                                                                            |

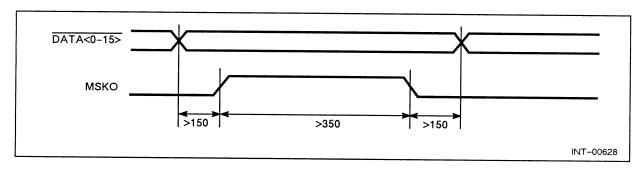

| ^мѕко   | Mask Out. This signal line is asserted low by the I/O bus controller during the execution of the Mask Out (MSKO) instruction, after the contents of the designated CPU accumulator have been placed on ^DATA<0-15>. Used to load the contents of ^DATA<0-15> into the interrupt disable flip-flops of all device controllers using the program interrupt system.                                                            |

| ^INTP   | Interrupt Priority. This signal line is always asserted true to the first device controller, on the I/O bus, using the program interrupt facility, and transmitted in series through each successive device controller. A device controller should not issue an asserted ^INTPOUT unless it is receiving an asserted ^INTPIN and is not requesting interrupt service.                                                       |

| INTA    | Interrupt Acknowledge. This signal line is asserted by the I/O bus controller during the execution of the Interrupt Acknowledge (INTA) instruction. If a device controller receives INTA while it is also receiving an asserted ^INTPIN and while it is requesting interrupt service, it should place its device code on ^DATA<10-15>.                                                                                      |

|         | Note that multiple INTAs can be received by a device before its interrupt is processed.                                                                                                                                                                                                                                                                                                                                     |

|         | Note that the I/O bus controller for I/O bus 0 will not assert INTA onto its I/O bus during the execution of the INTA instruction if one of the devices resident on the MCU/IOC/DRP board (primary asynchronous interface, real-time clock, programmable interval timer, and memory control unit and/or input/output channel error) requires interrupt service.                                                             |

| Data Ch | annel                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ^DCHR   | Data Channel Request. This signal line is asserted low by a device controller when it requires data channel service.                                                                                                                                                                                                                                                                                                        |

| ^DCHP   | Data Channel Priority. This signal line is always asserted true to the first data channel device controller, on the I/O bus, and transmitted in series through each device controller. A device controller should not issue an asserted ^DCHPOUT unless it is receiving an asserted ^DCHPIN and it is not requesting data channel service.                                                                                  |

| ^DCHA   | Data Channel Acknowledge. This signal line is asserted low by the I/O bus controller at the beginning of each data channel cycle. Should cause the device controller that is receiving an asserted ^DCHPIN signal and whose DCH REQ flip-flop is set.                                                                                                                                                                       |

|         | <ol> <li>The memory address (physical or logical) to be used for this transfer on signal lines<br/>^DATA&lt;2-15&gt; of the I/O bus.</li> </ol>                                                                                                                                                                                                                                                                             |

|         | <ol> <li>The additional DCH map slot address bits to be used for this transfer on signal lines<br/>^DS&lt;4-5&gt;, ^EXTDCH, and ^DATA0 of the I/O bus.</li> </ol>                                                                                                                                                                                                                                                           |

(continued)

Table 2-1 I/O Bus Signals

| Signal               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ^DCHA<br>(continued) | 3. And the type of transfer on signal lines ^DCHM0, and ^DS0 of the I/O bus.                                                                                                                                                                                                                                                                                                                                                                         |

| (continuou)          | Note that not all data channel device controllers use the additional map slot address bits and that some controllers do not use all of the additional map slot address bits (see "Data Channel Map Slot Selection" later in this chapter). Note also that not all data channel device controllers use ^DSO to specify the type of transfer. (See "Data Channel Transfer Modes" later in this chapter.)                                               |

| ^EXTDCH              | Extended Data Channel. This signal line is conditioned by the device controller whose DCH SEL flip-flop is set for memory mapping address selection. (See the information on signals ^DCHA and ^DS<4-5>.)                                                                                                                                                                                                                                            |

|                      | Note that not all data channel device controllers use ^EXTDCH as a map slot address bit. (See "Data Channel Map Slot Selection" later in this chapter.)                                                                                                                                                                                                                                                                                              |

| ^DCHM0               | Data Channel Mode. This signal line is conditioned by the device controller whose DCH SEL flip-flop is set to inform the I/O bus controller of the data channel transfer type to be performed. Used in conjunction with ^DS0 by some device controllers. (See the information on signal ^DS0.) (Also see description of data channel modes.)                                                                                                         |

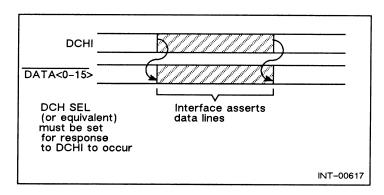

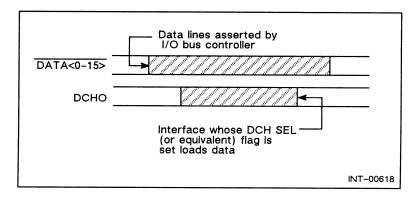

| DCHI                 | Data Channel Input. This signal line is asserted by the I/O bus controller for data channel input (^DS0 = 0, ^DCHMO = 1) and for the write portion of a read-modify-write transfer (^DS0 and ^DCHMO both = 1). Should cause the device controller whose DCH SEL flip-flop is set to place the contents of its input register on ^DATA<0-15>.                                                                                                         |

| DCHO                 | Data Channel Output. This signal line is asserted by the I/O bus controller for data channel output (^DS0 and ^DCHMO = 0) and for the read portion of a read-modify-write transfer (^DS0 and ^DCHMO both = 1), after the data word has been placed on ^DATA<0-15>. Should cause the priority-selected device controller to load the data from ^DATA<0-15>.                                                                                           |

| System C             | control                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IORST                | I/O Reset. This signal line is asserted by the I/O bus controller during the I/O Reset (IORST) instruction or when a Reset function occurs. IORST is also issued prior to central processing unit operation at powerup. This signal should be used to initialize the machine state of all device controllers in the system.                                                                                                                          |

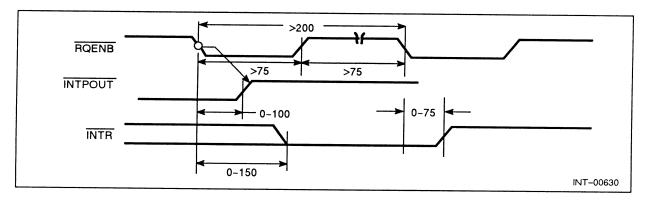

| ^RQENB               | Request Enable. This signal line is asserted low by the I/O bus controller to synchronize program interrupt and data channel requests from all device controllers. In any device controller, 'INTR and 'DCHR should be clocked only on the transistion from high to low level of 'RQENB. I/O bus controllers do not assert 'RQENB while an Interrupt Acknowledge INTA instruction is being executed (see "Interrupt Request" later in this chapter). |

(concluded)

# Programmed I/O Protocol

Programmed input/output transfers are controlled by a unique signal on the I/O bus. When selected, device controllers must respond to programmed input/output transfer signals as described in the following sections.

#### **Device Selection**

Every programmed input/output instruction includes a 6-bit device code that uniquely references the device controller involved in the transfer. During input/output instruction execution, the device select lines (^DSO through ^DS5) carry the contents of the low- order 6 bits of the instruction, which is the device code. The device controller must not assert the ^DATA<0-15> lines of the bus or initiate any other function as a result solely of the device select lines. Rather, the selected device controller should respond only to the assertion of control signals on the I/O bus when it is selected.

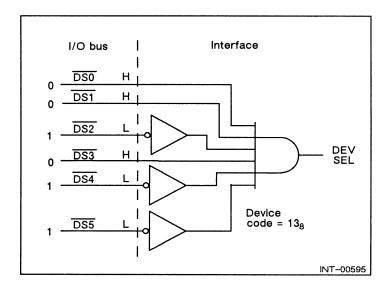

A device controller can decode the device select lines in several ways. The device select lines corresponding to the bit positions containing a 1 in the device controller's device code could be inverted and an And function performed on the resultant 6 lines, as shown in Figure 2-2 for device code  $13_8$ .

Figure 2-2 Single Device Code Selection Network

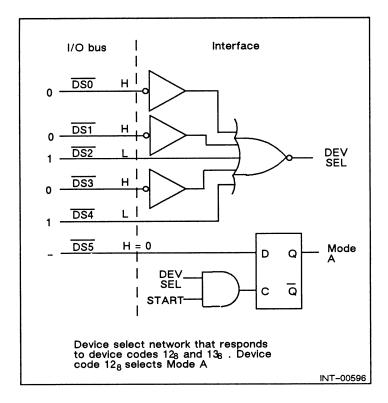

Similarly, the lines corresponding to 0s could be inverted and the six lines applied to a NOR gate. There are other possibilities; but the two important details are that the lines are asserted low and that 'DSO is the high-order bit of the device code. Note that it is possible to have the device controller respond to more than one device code by decoding fewer than six lines. The remaining lines might be clocked into a register to select a particular device controller mode as shown in Figure 2-3.

014-001856

Figure 2-3 Multiple Device Code Selection Network

#### **Assigning Device Codes**

There are a number of factors to be considered when assigning a device code to a device controller. A 6-bit device code allows 64 possible codes, 1 to 77<sub>8</sub>. Device code 77<sub>8</sub> is assigned to the central processing unit to implement such special functions as Mask Out and Interrupt Acknowledge; hence it cannot be assigned to a device controller. In addition, several device codes are assigned to resident devices and a number of programming considerations restrict the use of device codes as assigned by Data General and used in all Data General software. (Standard ECLIPSE device codes can be found in the ECLIPSE MV/Family (32-Bit) Systems Principles of Operation manual as well as the Principles of Operation Supplement for your specific system). When you assign a device code to a custom device controller, it is important to consider these reserved device codes and any other devices that are currently in the system or may be installed in the future.

NOTE: Reserved or assigned device codes can be used as long as those codes are not already in use for devices attached to your system.

#### **Data Transfer Signals**

Six data transfer signals of the I/O bus move a word or part of a word under direct program control from a device controller to central processing unit accumulators and vice versa.

**2–8** 014–001856

#### Data Input

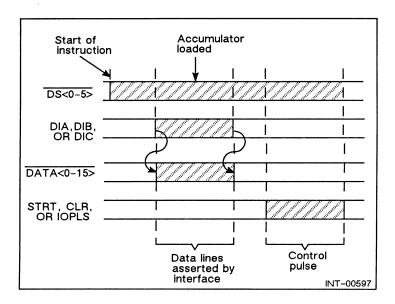

The three programmed data input instructions — Data in A, B, and C (DIA, DIB, and DIC) — allow data to be transferred from up to three distinct sources per device code in the device controller and loaded into any one of the four CPU accumulators. Additionally, if specified in the instruction, one of the following flag control signals will be issued by the I/O bus controller to control the status flags or other device controller functions: Start, Clear, or I/O IO Pulse.

The execution of a data input instruction consists of two parts. The first is the data transfer, followed by the (optional) flag control pulse. Three signals are used for the data input transfer, one for each of the three possible sources in the device controller. Through the use of three separate signals, the need for a decoding network in the device controller is avoided.

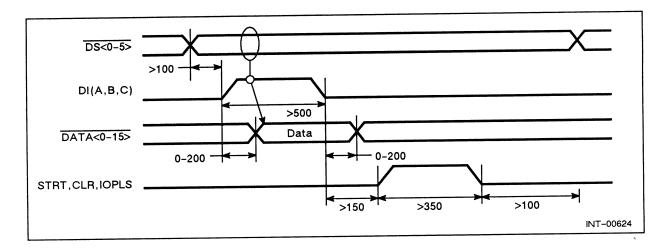

During the first half of data input instruction execution, one of the three transfer control signals — DIA, DIB, or DIC — is asserted on the I/O bus by the I/O bus controller, as shown in Figure 2-4. This signal should be used by the addressed device controller to cause data from the proper sources to be asserted on the ^DATA<0-15> lines of the I/O bus. After a time delay, the I/O bus controller will transfer the information on the ^DATA<0-15> lines into the CPU accumulator specified by the instruction and remove the transfer control signal.

NOTE: Because all device controllers are wired to the I/O bus in parallel, it is extremely important that only the device controller referenced by the device select code assert any of the ^DATA<0-15> lines — and then only in response to the transfer control signal.

During the second half of the instruction execution, the appropriate flag control pulse — Start, Clear, or IO Pulse — is asserted. These pulses are specified in the flag control (f) field of the instruction. The response of the device controller to each of these signals will be discussed later.

Figure 2-4 Data In Sequence

014-001856

#### **Data Output**

The three programmed data output instructions — Data Out A, B, and C (DOA, DOB, and DOC) — transfer data from any one of the four CPU accumulators through the I/O bus controller to one of up to three destinations per device code in the device controller. Additionally, if specified in the instruction, a flag control signal — Start, Clear, or IO Pulse — will be issued by the I/O bus controller to control the status flags or other device controller functions.

The execution of a data output instruction consists of two parts: the data transfer, followed by the (optional) control pulse. Three signals are used for the data output transfer, one for each of the three possible data destinations in the device controller. Through the use of three separate signals, the need for a decoding network in the device controller is avoided. Note that the three destinations used for data output needn't have any relation to the three data sources used for data input.

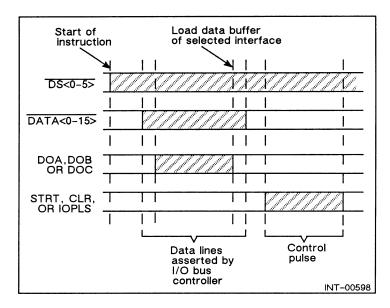

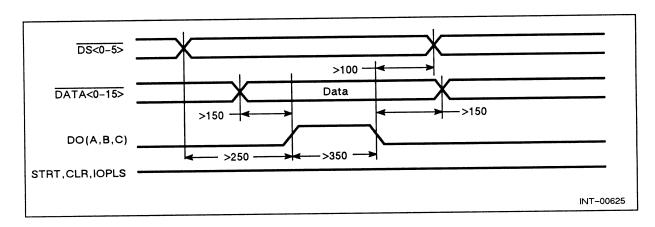

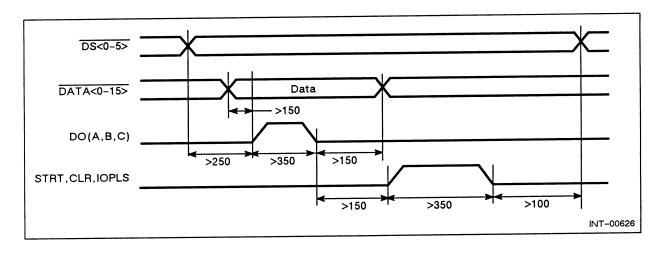

As shown in Figure 2-5, the I/O bus controller asserts the ^DATA<0-15> lines with the contents of the CPU accumulator specified in the instruction. After allowing time for the data to propagate down the I/O bus and for the lines to settle, the I/O bus controller asserts one of the three transfer control signals — DOA, DOB, or DOC. This signal should be used by the selected device controller to gate the contents of the ^DATA<0-15> lines to the proper destination and to load a register. After removing the transfer control signal, the I/O bus controller will remove the data from the ^DATA<0-15> lines.

NOTE: Because all device controllers are wired to the I/O bus in parallel, it is extremely important that no device, including that referenced by the device select code, be allowed to assert any of the ^DATA<0-15> lines during the data output instruction.

During the second half of the instruction execution, the appropriate flag control pulse - Start, Clear, or IO Pulse - is asserted. These pulses are specified in the flag control (f) field of the instruction. The response of the device controller to each of these signals will be discussed later.

Figure 2-5 Data Out Sequence

2–10

#### I/O Skip

The operation of most peripherals is not synchronous to the operation of the CPU. Because of its faster processing rate, the CPU will generally have to wait for the completion of a peripheral's operation. It is usually important for the CPU not to issue any new instructions to the peripheral until the peripheral has completed its previous operation. This asynchronous relationship between the CPU and peripheral requires that the CPU be able to test the status of the peripheral.

The I/O Skip (IOSKP) instruction allows the program to test the state of two I/O bus lines: ^SELB and ^SELD. Whenever a device controller recognizes its device code on the device select lines, as discussed above, it should assert the ^SELB and/or ^SELD lines depending on the internal state of the device controller. (Ordinarily, ^SELB will be asserted if the Busy flag is set, and ^SELD will be asserted if the Done flag is set.) During the execution of the I/O Skip instruction, the I/O bus controller passes the content of these two lines to the CPU for testing. The CPU checks the state of the appropriate line and skips the next sequential instruction if the line matches the condition specified in the instruction.

The test condition is specified in the test t field of the instruction as shown in Table 2-2.

| Test Field | Mnemonic | Next Instruction Skipped If |

|------------|----------|-----------------------------|

| 00         | BN       | ^SELB = L                   |

| 01         | BZ       | ^SELB = H                   |

| 10         | DN       | ^SELD = L                   |

| 11         | DZ       | ^SELD = H                   |

Table 2-2 Test Conditions

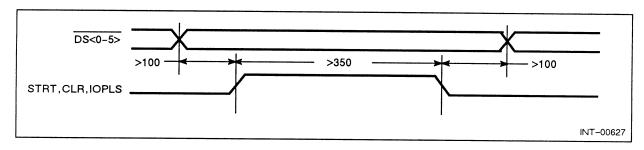

### Start, Clear, I/O Pulse

During the second half of the instruction execution, the appropriate flag control pulse - Start, Clear, or IO Pulse - is asserted. These pulses are specified in the flag control (f) field of the instruction. The response of the device controller to each of these signals will be discussed later. Though a convention is followed in using these signals in Data General device controllers, as explained below, the designer should realize that the signals may be used for virtually any purpose.

#### **Busy/Done Network**

In Data General device controllers, two flags — Busy and Done — carry elementary status information needed by the program. Any time a device controller detects its device code on the device select lines, it asserts the **SELB** line if its Busy flag is set and/or **SELD** if its Done flag is set. During the execution of an *I/O Skip* (IOSKP) instruction, the I/O bus controller passes the content of these two lines to the CPU for testing. The CPU checks the state of the line as specified by the test control (t) field of the instruction and skips the next sequential instruction if the line matches the condition specified in the instruction.

014–001856

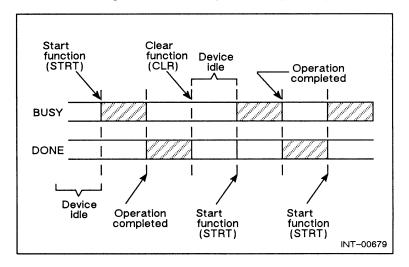

Although the significance of the flags may vary somewhat depending on the particular device controller in question, they do carry a similar meaning in many cases. The Busy flag generally indicates that the device is currently processing data or waiting for some response from an external system. When this flag is set, any interference from the program, such as an attempt to transfer information to this device, may produce unpredictable results. The Done flag indicates that the device has completed an operation and is awaiting a response by the program. In many devices, it is important that this response come within a maximum time period to prevent a degradation of system performance. See Figure 2–6 for Busy/Done sequencing.

Figure 2-6 Busy/Done Sequencing

In addition to conveying status information to the program, these flags can be used as switches by the program to control the device controller. Generally, the *Start* pulse causes the Busy flag to be set and the Done flag to be cleared, initiating device controller operation. At the completion of the operation, a signal originating in the device controller sets Done and clears Busy. If at any time the *Clear* pulse is issued by the I/O bus controller, both flags should be cleared.

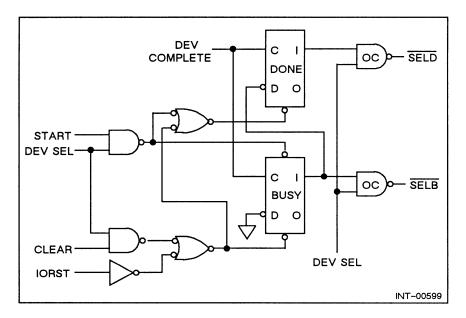

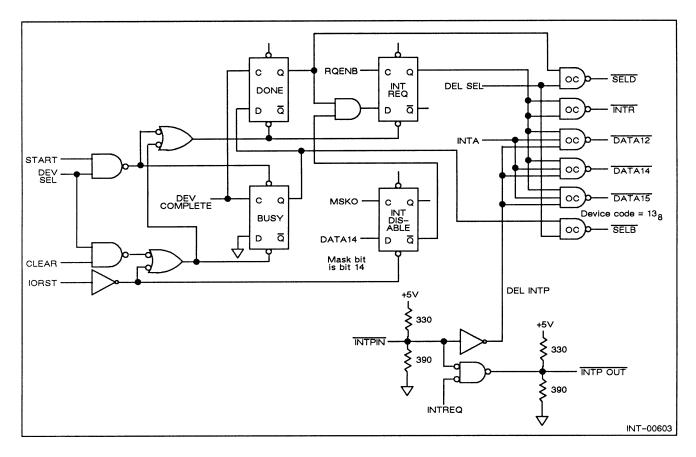

Figure 2–7 shows one implementation of the Busy/Done network. The **IORST** signal clears both the Busy and Done flags directly. Signals generated by the flag control function part of an I/O instruction affect the flags only if the device has recognized its device code on the device select lines. When the device completes its operation, it generates a completion signal, DEV COMPLETE, that clears the Busy flag and sets the Done flag. The signal need not act on both flags directly; it can just as well clear the Busy flag, whose state change sets the Done flag. Note that in the configuration shown here, the *D* input to the Done flag is the output of the Busy flag. Therefore, the completion signal will not set the Done flag if the program has previously cleared the Busy flag.

**2–12** 014–001856

Figure 2-7 Typical Busy/Done Network

### **Program Interrupt System**

The program interrupt system provides a device controller with a convenient means of notifying the central processing unit that the controller requires service by the program.

#### Interrupt Request

A device controller issues a program interrupt request by asserting the **INTR** line of the I/O bus. The CPU checks this line at the end of every instruction and at specific points during the execution of lengthy instructions. If the interrupt line is asserted (and the CPU's Interrupt On ION is 1), it executes the program interrupt function. The interrupt in no way affects the device controller itself; any action to actually service the device must be the result of the software interrupt handler.

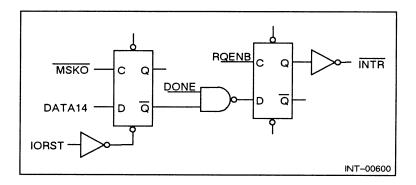

The signal, ^RQENB, generated by the I/O bus controller is used to clock the interrupt requests. The usual convention is to use the transistion of ^RQENB from a high to low level to clock the interrupt request (INTR) flip-flop when the peripheral has set its Done flag and the device controller does not have its interrupts disabled. The INTR flip-flop in turn drives the ^INTR line. It is very important that INTR be asserted and removed synchronous with the transistion from high to low level of ^RQENB.

I/O bus controllers do not assert ^RQENB while an *Interrupt Acknowledge* (INTA) instruction is being executed. This ensures that no higher priority device sets its interrupt and applies its device code to the I/O bus during the INTA signal. It could be possible that the time might not be long enough to ensure that the device code is properly received by the I/O bus controller.

014-001856

#### Interrupt Disable

In addition to the three data output transfer control signals, there is a signal, ^MSKO, that functions in much the same way. This signal allows a 16-level priority system to be established for the program interrupt facility. The signal, ^MSKO is issued during the data transfer portion of a *Data Out B* (DOB) instruction when a device code of 77<sub>8</sub> is specified (CPU).

Conventionally, each device controller using the interrupt system is assigned a hardware priority level corresponding to 1 of the 16 bits of a data word. When the ^MSKO signal is received by the device controller (regardless of the device code), an Interrupt Disable flag (INT DISABLE) should be loaded from the ^DATA<0-15> signal corresponding to the priority assignment of that device controller, as shown in Figure 2-8. Whenever this INT DISABLE flag is set, the device controller should be inhibited from issuing an interrupt request. Additionally, if the device controller is issuing an interrupt request when the INT DISABLE flag is set, the request should be removed on the next transistion from high to low level of ^RQENB.

Figure 2-8 Typical Priority Mask Bit Circuit

#### Interrupt Priority

There is an elementary hardware priority assignment on the I/O bus that arbitrates between two or more device controllers requesting interrupt service at the same time. In the event of simultaneous interrupt requests, this priority system grants service to the device controller that is requesting service and is closest to the I/O bus controller on the I/O bus.

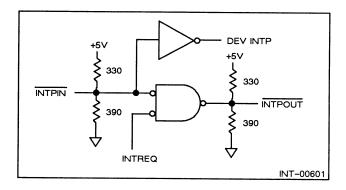

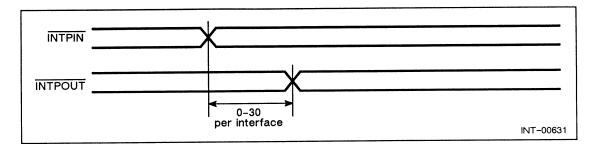

The interrupt priority signal should be passed through a priority network in every device controller that uses the program interrupt facility. This signal, which must be passed undisturbed by other device controllers (and any printed circuit boards installed in device controller slots of the chassis), is called 'INTPIN as it enters each device controller and 'INTPOUT as it leaves. For each I/O bus implemented, 'INTPIN starts on the chassis' backpanel at the first I/O printed circuit board slot of the I/O bus(es) as a low (asserted) signal, but it is pulled high to succeeding device controllers by any device controller that requests interrupt service. Any device controller that receives a high 'INTPIN signal should pass a high 'INTPOUT to the device controllers further along the bus.

The circuit in Figure 2–9 shows the suggested implementation of this priority network. In many cases, more than one device controller using the program interrupt facility will be built on a single board. Here, each device controller built on the board will

2–14

require its own priority network. As many elements as needed, each similar to that shown below, will be chained together, with the 'INTPOUT signal of one feeding 'INTPIN of the next. Note that the terminating resistors shown are used on the signals that enter and leave the board.

Figure 2-9 Typical Interrupt Priority Chain

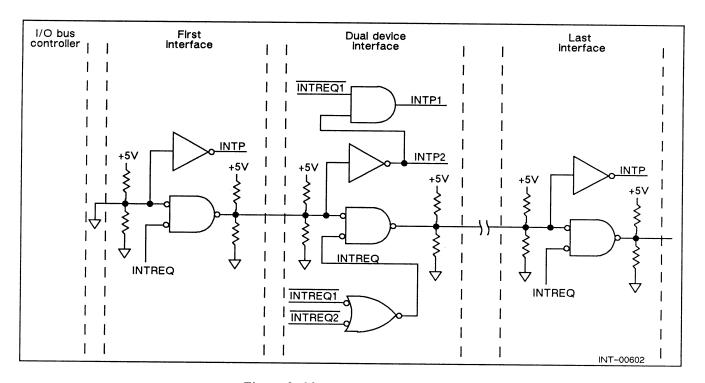

Timing on this interrupt priority chain can be critical and becomes especially so for large systems with many device controllers. Often it is possible to build several device controllers on a single board. In these cases, the propagation time can be significantly reduced by replacing the priority chain on such a board with two separate chains. One chain, consisting of a single network element, determines the priority of the entire board and quickly passes the **INTP** signal on to the next board. A separate chain determines the priority of the various device controllers on the board. See Figure 2–10.

Figure 2–11 shows a typical interrupt control circuit as implemented in each device controller.

Figure 2-10 Interrupt Priority Chain

Figure 2-11 Typical Interrupt Control Circuit

#### Interrupt Acknowledge

Once the central processing unit has received an interrupt request and transferred control to the interrupt service routine, the software must service the device controller that caused the interrupt. Before the program can even attempt to service the device controller, it must determine which device controller did, in fact, cause the interrupt. The simplest way that this can be achieved is by the use of the *Interrupt Acknowledge* (INTA) instruction. This instruction is equivalent to a *Data Input B* (DIB) instruction with a device code of 77<sub>8</sub> (CPU). This instruction executes as a data input transfer instruction, but the I/O bus controller asserts the INTA signal on the I/O bus during the data transfer portion of the instruction.

Note that the I/O bus controller for I/O bus 0 will not assert INTA onto its I/O bus during the execution of the *Interrupt Acknowledge* (INTA) instruction if one of the devices resident on the MCU/IOC/DRP (MID) board requires interrupt service. Devices that are resident on the MID board are the primary asynchronous interface, the real-time clock, the programmable interval timer, the memory control unit, and input/output channel error.

When the INTA signal is received by a device controller (regardless of device code), the condition of the 'INTPIN line to that device controller should be checked. If this line is asserted and the device controller is currently issuing an interrupt request, it should assert its device code on 'DATA<10-15> of the I/O bus for the duration of the INTA signal. At the end of the INTA period, the I/O bus controller transfers the

2–16

I/O channel code and device code to the CPU. The CPU then loads the I/O channel code and device code into the specified CPU accumulator.

# **Data Channel**

Unlike programmed input/output transfers, which are each controlled by one unique signal on the I/O bus, data channel transfers are somewhat more complex. The interaction between the I/O bus controller and the device controller is much more involved, because of the number of functions performed for each transfer. Unlike the design of a programmed I/O device controller, where certain liberties can be taken in the designed response to a bus signal, the design of a data channel device controller is relatively restricted, and we recommend that such a design correspond to the following description.

#### **Data Channel Request**

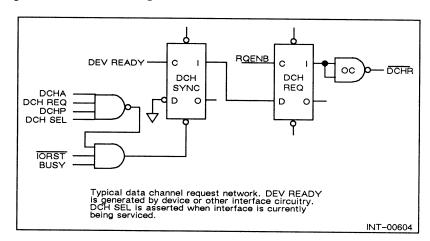

A device controller issues a data channel request by asserting the ^DCHR line of the I/O bus. Unlike interrupts, the I/O bus controller services a data channel request completely without software intervention.

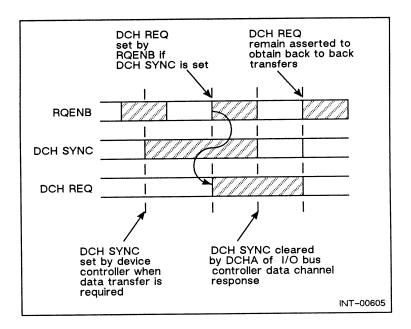

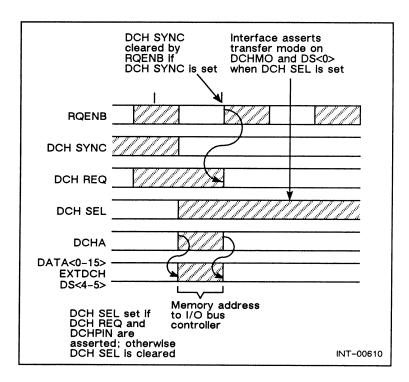

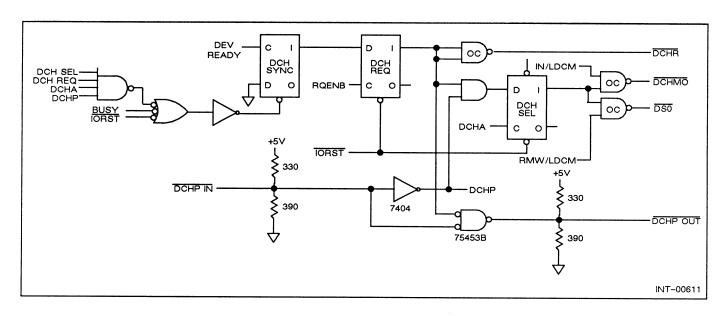

The signal, ^RQENB, generated by the I/O bus controller is used to clock the data channel requests in the same manner as the interrupt requests. The usual convention is to use the transistion from high to low level of ^RQENB to clock the state of a flip-flop, controlled by the device controller (DCH SYNC in Figure 2-12), into a data channel request (DCH REQ) flip-flop, which in turn drives the ^DCHR line.

NOTE: It is very important that **^DCHR** be clocked only on the transistion from high to low level of **^RQENB**.

Figure 2-12 Typical Data Channel Request Circuit

When the I/O bus controller sees ^DCHR asserted, it transfers data to or from the highest priority controller requesting service. Just before the end of every data channel transfer, the I/O bus controller pulses the ^RQENB signal again. And if the ^DCHR signal is still asserted at the end of the current transfer, the I/O bus controller performs data channel transfer to the highest priority controller that is still requesting data channel service. The I/O bus controller continues to perform data channel transfers in this way until no controller on the I/O bus is requesting data channel service. Figure 2–13 shows the timing sequence required for data channel transfers.

Figure 2-13 Typical Data Channel Sequence

#### **Data Channel Priority**

There is an elementary hardware priority assignment system on the I/O bus that arbitrates between two or more device controllers requesting data channel service at the same time. In the event of simultaneous data channel requests, this priority system grants service to the device controller that is requesting service and is closest to the I/O bus controller on the I/O bus.

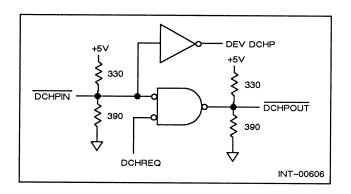

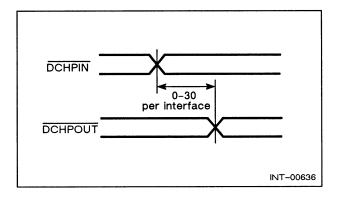

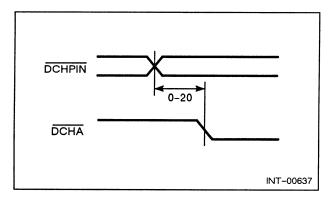

The data channel priority signal should be passed through a priority network in every device controller that uses the data channel. This signal, which must be passed undisturbed by other device controllers (and any printed circuit boards installed in device controller slots of the chassis), is called ^DCHPIN as it enters each device controller and ^DCHPOUT as it leaves. For each I/O bus implemented, ^DCHPIN starts on the chassis backpanel, immediately adjacent to the respective I/O bus controller board(s), as a low (asserted) signal, but it is pulled high to succeeding device controllers by any device controller that requests data channel service. Any device controller that receives a high ^DCHPIN signal should pass a high ^DCHPOUT to the device controllers further along the bus.

The only device controller that should respond to the I/O bus controller's data channel signals is that which is requesting data channel service and is receiving a low level **^DCHPIN**; that is, the device controller closest to the I/O bus controller, on the I/O bus, that is requesting data channel service.

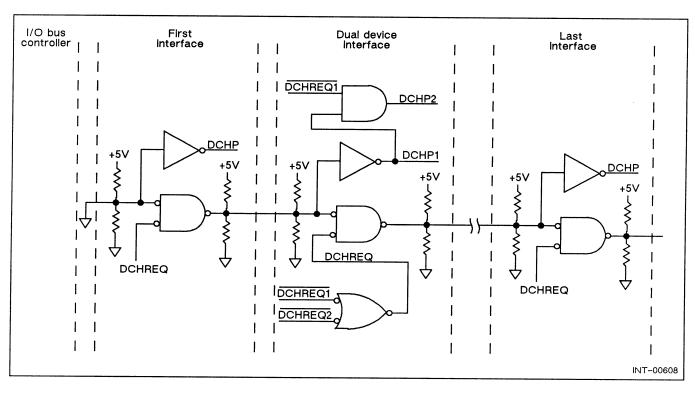

The circuit shown in Figure 2–14 shows the suggested implementation of this priority network. In some cases, more than one device controller using the data channel facility will be built on a single board. Here, each device controller will require its own priority network. As many elements as needed, each similar to that shown below, will be chained together, with the ^DCHPOUT signal of one feeding ^DCHPIN of the next one. Note that the terminating resistors shown are used on the signals that enter or leave the board.

Figure 2-14 Typical Data Channel Priority Circuit

Timing on this data channel priority chain can be critical and becomes especially so for large systems with many device controllers. Often it is possible to build several device controllers on a single board or in a single external chassis. In these cases the propagation time can be significantly reduced by replacing the priority chain on such a board with two separate chains. One chain, consisting of a single network element, determines the priority of the entire board and quickly passes the ^DCHP signal on to the next board. A separate chain determines the priority of the various device controllers on the board. (See Figure 2–15).

Figure 2-15 Data Channel Priority Chain

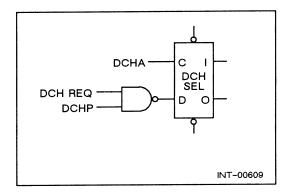

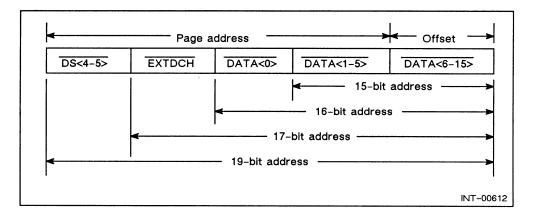

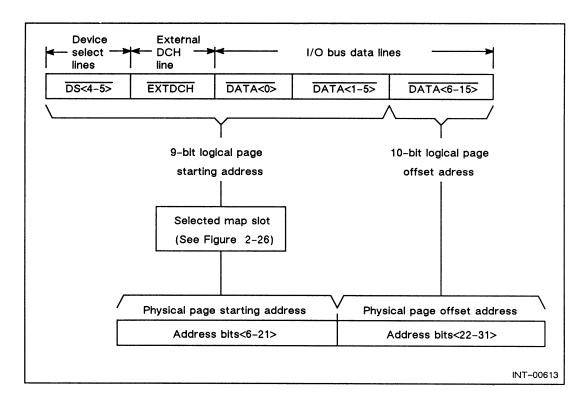

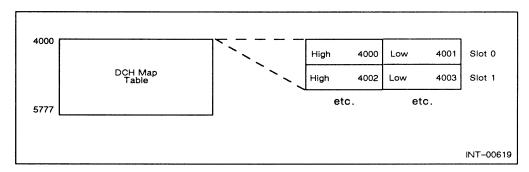

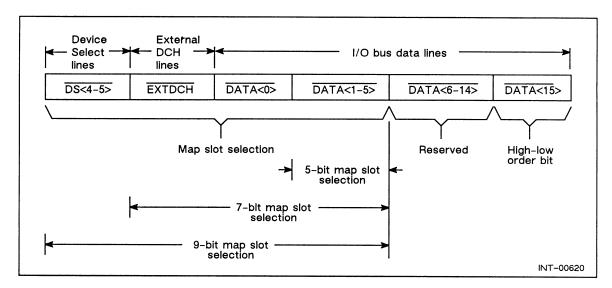

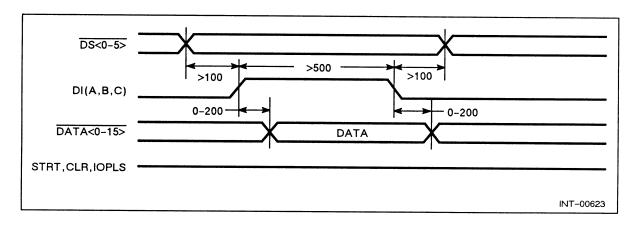

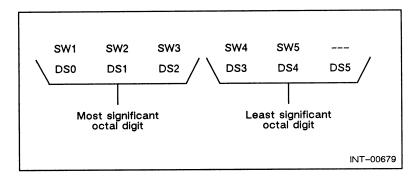

# Data Channel Acknowledge